# PART B

# COLLABORATIVE PROJECT

# Table of Contents

| B1Concept and objectives, novelty and foundational character, specific contribution |    |

|-------------------------------------------------------------------------------------|----|

| to S&T, S/T methodology and work plan                                               | 2  |

| B1.1 Concepts and Objectives                                                        | 2  |

| B1.2 Novelty and foundational character                                             | 3  |

| B1.3 Specific contribution to progress in science and technology                    | 5  |

| B1.3.1 The goal of designing energy-efficient systems                               | 5  |

| B1.3.2 Is energy transparency possible?                                             | 6  |

| B1.3.3 What optimizations are enabled by energy transparency?                       | 9  |

| B1.3.4 What are the implications for tools and methods?                             | 11 |

| B1.3.5 Further research beyond the project                                          | 12 |

| B1.3.6 Project Strategy and Research Areas                                          | 12 |

| B1.3.7 Related Projects                                                             | 13 |

| B1.4 S/T Methodology and Associated Work Plan                                       | 14 |

| B1.4.1 Overall strategy and general description                                     | 14 |

| B1.4.2 Timing of work packages and their components                                 | 19 |

| B2Implementation                                                                    | 20 |

| B2.1 Management Structure and Procedures                                            | 20 |

| B2.2 Beneficiaries                                                                  | 22 |

| B2.2.1 Roskilde University                                                          | 22 |

| B2.2.2 University of Bristol                                                        | 24 |

| B2.2.3 IMDEA Software Institute                                                     | 26 |

| B2.2.4 XMOS Limited                                                                 | 28 |

| B2.3 Consortium as a Whole                                                          | 28 |

| B3Impact                                                                            | 30 |

| B3.1 Strategic Impact                                                               | 30 |

| B3.1.1 Transformational Impact on Science, Technology and/or Society                | 30 |

| B3.1.2 Expected Impacts Listed in the Work Programme                                | 35 |

| B3.2 Plan for the use and Dissemination of Foreground                               | 38 |

| B3.2.1 Dissemination                                                                | 38 |

| B3.2.2 Exploitation                                                                 | 40 |

| B3.2.3 Management of Knowledge and Intellectual Property                            | 42 |

| B4Ethical Issues                                                                    | 42 |

# B1 Concept and objectives, novelty and foundational character, specific contribution to S&T, S/T methodology and work plan

# **B1.1** Concepts and Objectives

**Overall Goal.** This project proposes an energy-aware system development approach covering hardware, software and the run-time environment. The central goal is to make *energy usage transparent* through the system layers, thus enabling optimizations both during code development and at run-time.

The project work packages will develop novel program analysis and energy modelling techniques. Tools incorporating these techniques will enable energy optimizations both during code development and at run-time, helping to promote energy efficiency to a first-class software design objective. The project will also develop a concept of optimality and a set of <u>benchmarks</u> allowing measurement of energy efficiency with respect to the minimal energy achievable by optimal utilization of existing hardware.

Motivation and Novelty. Lack of energy transparency in today's system development tools means that much of the potential energy saving available from power-efficient hardware is wasted. The project departs from the approach of today's systems and development tools because energy transparency is at odds with a basic principle in modern software engineering – the desire to abstract away machine-level details in high-level code in the interests of portability, understandability and software reuse. By contrast, energy transparency requires making visible the effects of energy-saving features of modern processors. The project targets outcome (c) of Objective ICT-2011.9.8, namely to address software models and programming methodologies supporting the strive for the energetic limit (e.g. energy cost awareness or exploiting the trade-off between energy and performance/precision).

**Key Techniques to Achieve Energy Transparency** The realization of the project vision of energy transparency relies on innovation in two main areas.

- Program analysis concerns the derivation of energy information from software, which may refer to whole programs, individual procedures, statement blocks or lines of code, programs in high-level languages as well as machine code. Static analysis concerns deriving such information without executing the program, while dynamic analysis obtains information on energy usage from running programs. In general, dynamic analysis infers precise information for a finite number of execution traces, while static analysis infers approximated information for all possible execution traces. Thus, it is a major challenge to develop novel analysis techniques that bring together the best of static and dynamic approaches for each system layer and also to infer information that relates energy consumption with precision and performance.

- Advances in combined hardware-software energy modelling are needed to support effective program analysis. Traditionally, energy models are restricted to the level of machine instructions, and in particular to assign energy consumption values or ranges to individual machine instructions. We will develop methods of constructing energy models of high-level programming abstractions like blocks of code, functions, APIs and interfaces, building on combinations of semantic interpretation and information extracted at run-time. We will also study how to make higher-level models more precise incorporating information about the execution context, like execution history, and program and processor state.

# Promoting Energy Efficiency to a First-Class Design Goal

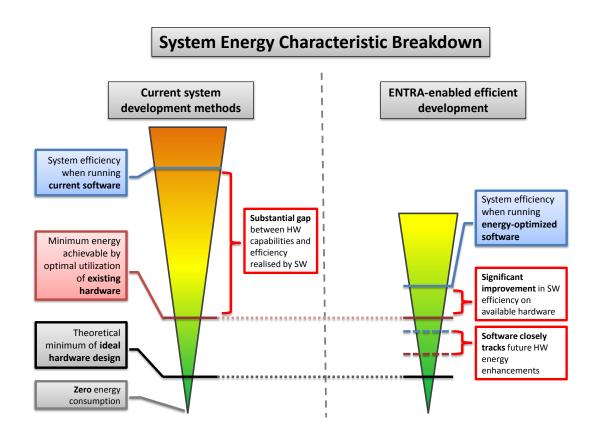

- Optimization: Towards Energy Optimality A recent estimate by Intel states that energy savings by a factor of 3 to 5 could be achieved using software optimizations alone [22]. One of the keys to achieving this saving lies with equipping all stages of the software lifecycle with information on the energy-saving capabilities of the underlying hardware and the energy costs of performing various operations with that hardware. The project will establish the maximum energy saving for a given hardware/software combination and apply optimizations that push the energy efficiency of this system towards this limit. This will include annotations and development methods utilized by software engineers, transformations applied during compilation, and task management strategies used at run-time. This will enable software engineers to tackle energy-efficiency directly, rather than as a side-effect of other efforts. Figure 1 summarises the vision of optimality towards the limit, both for a given hardware platform and with respect to the theoretical limit.

- Verifying Energy Budgets Verification compares actual system properties with required properties in order to prove them or to detect inconsistencies. Being able to certify that a given energy budget is met, while maintaining a given level of quality of service (regarding precision or performance) is an important challenge. First, energy related information depends on different system and data parameters, so that a rich energy consumption semantics, that represents energy as a function of such parameters, is needed. Second, complex function comparison operations are needed in order to compare analysis information against specifications. The result of such comparison should ideally give preconditions under which a given specification is met or not. Another challenge is to find the causes of an energy consumption assertion violation, and help the system developer to redesign it.

# **Project Objectives**

- 1. Establish energy modelling (WP2) and analysis techniques (WP3) that support energy transparency through the system layers.

- 2. Develop prototype tools enabling engineers to understand and quantify the impact of design decisions on energy (WP1).

- 3. Enable software engineers to express and verify properties of the system throughout its lifecycle relevant to energy (including precision and performance) (WP3).

- 4. Develop optimization techniques both at design and run-time enabled by energy transparency (WP4).

- 5. Develop energy benchmarking techniques (WP5) and a concept of energy optimality for a given application and hardware platform against which project case studies can be evaluated (WP6).

# B1.2 Novelty and foundational character

Why achieving energy transparency is difficult Energy transparency is an ambitious target, since the natural trend in software engineering is to move software design further and further from the machine level towards more abstract concepts, with high-level languages, abstract data types and classes and reusable generic libraries, executed by layers of interpretation or compilation. This means that the level at which energy is actually consumed in a system – transistor activity and state preservation in silicon – is far removed from the level at which designers and system users usually think

and work. Static analysis of energy consumption of a high-level program thus involves either combining several stages of analysis, or analysing the program with respect to more complex semantics than usual. Similarly, dynamic energy analysis faces the inverse problem of interpreting measured energy at the compiled machine code level in terms of the high-level program source.

A further challenge is that energy usage is typically dependent on program input and other external factors including hardware parameters like processor clock speed; the results of static analysis of energy consumption are thus required to be parameterised by these external variables whose values might not be known at analysis time.

Energy efficiency as a first-class software design goal Achieving energy transparency throughout a system will open up the possibility of promoting energy efficiency to a first-class software design principle and goal. This promotion implies that desired energy usage can become part of the specification of an application, and can be considered right from the start of the design process and throughout all stages of software development. In particular, the possibility of formally verifying that a program meets an energy budget becomes feasible. At present, by contrast, energy consumption is measured in the final implementation, and if a program does not meet some energy target, the only choice is to reimplement the program and try again, potentially at great cost.

A whole-systems approach to energy management Furthermore, energy transparency will enable a range of run-time optimizations that are inconceivable at present, deciding dynamically how available energy in a system can be utilized optimally. Energy transparency enables to combine predictive models of energy usage of individual programs in the context of overall system usage.

As a rough analogy, it will be possible to apply ideas similar to those in "smart grids" to the energy management of a computer system. The run-time system of a software built using techniques from energy transparency will have access to models of energy-usage and can effectively exploit a range of dynamic controls and scheduling possibilities to reduce overall energy usage. While there are current research efforts directed at drastically reducing the energy consumption when a system is idling, this is only one approach to energy saving. The "whole-systems" enabled by energy transparency not only allows to increase idling periods and improve idle tasks, but also allows to design systems where energy management is improved by judiciously amortizing and smoothing the use of resources.

Figure 1: ENTRA Vision of Energy Optimization towards the Limit

# B1.3 Specific contribution to progress in science and technology

In this section we discuss the main scientific challenges and advances needed to make energy-efficiency a first-class design goal.

# B1.3.1 The goal of designing energy-efficient systems

Why is it a problem? Today's software engineering approaches produce systems that are far from energy-optimal, even though energy consumption is a major concern, especially in embedded systems. Traditionally, researchers and engineers work within one or perhaps two layers of the system stack with very limited overlap, e.g. software engineers, computer architects or hardware designers. Energy-efficient computing, however, is a challenge that requires considering the entire system stack vertically (as opposed to horizontally), from application software and algorithms, via programming languages, compilers, instruction sets and micro architectures, down to the design and manufacture of the hardware.

In an attempt to address this, various software-controllable energy-saving features have been developed, such as DVFS, where power modes can be selected via embedded software drivers or application software. However, many if not most applications, especially if designed in high-level languages, are simply unable to take advantage of these features and so the application will not see any low-power benefits. The designer of the software has no way to understand or exploit the available controls.

While hardware can be designed to save a modest amount of energy, the potential for savings are far greater at the higher levels of abstraction in the system stack [22]. The greatest savings are expected from energy-efficient software. Addressing the challenge of energy-efficient computing requires energy transparency over the entire system stack.

# B1.3.2 Is energy transparency possible?

The essential requirement is that energy usage should be visible at the level at which software is designed or used. One could imagine an over-simplified view of energy transparency as an interactive development environment that colours source code according to how much energy it consumes – red for the energy-expensive code and green for the "cool" parts. Despite the over-simplification we can use it to identify the essential components of a potential solution that enables the energy consumption at hardware level to be immediately visible at source code level. These components are:

- analysis of programs with respect to energy usage, performance and precision;

- energy modelling at low and high level;

- a common assertion language as an integrating framework;

**Program analysis.** Static analysis of source code derives information about run-time behaviour without actually running the code. Among other run-time properties, analysis of resource usage of computations has been the subject of previous research. Typically, execution time and memory usage are analysed, but more recently analysis of other resources including energy, bits sent or received, number of accesses to a database, or monetary units spent have also been the subject of static analysis. Furthermore, information from static analysis plays an increasingly central role in optimisation, debugging and verification tools.

Abstract interpretation as a generic analysis framework. The set of possible computations of a program is usually extremely large, and therefore practical automatic analysis tools have to make approximations to program behaviour. A systematic approach to static analysis has been developed over the past 30 years, based on the principles of abstract interpretation [16]. Abstract interpretation provides an approach for implementing a sound approximate execution of a program from a specification of the concrete semantics of the language of the program together with a so-called abstraction function. The abstraction function typically abstracts away things that are not relevant to the analysis in question. For example, in an analysis focusing on energy usage, an abstraction function would abstract away aspects of a state not relevant to energy consumption.

Abstract interpretation has been applied to programs ranging from assembler code and embedded systems code through to high-level declarative languages and specification languages. Tools based on abstract interpretation are being applied in industrial applications (see e.g. [20]).

Time and complexity analysis. The problem of automatically estimating the amount of time a program will take to run, in relation to the size of the input, is sometimes called complexity analysis or cost analysis and will form a basis for energy analysis. Techniques exist for inferring the complexity in terms of (an upper bound on) the number of execution steps, reductions, resolution steps or function calls (depending on the programming paradigm) of a given program. Often, this involves analysing a step-counting program transformed from the original program. The established approach is to set up recurrence relations and obtain solutions of them as closed form complexity cost functions. Relevant previous work includes [18, 17, 19, 54, 9, 28, 17, 18, 19, 49, 32, 2, 1]. It is notable that the results of such analyses are parameterized expressions, that is, they express the number of steps as a function of input data size.

In some applications step-counting is not sufficiently precise, especially where there are real-time constraints, and accurate timing information is needed. A number of static analyses are aimed at worst case execution time (WCET), usually for imperative languages in different application domains. These have produced precise timing models (see, e.g., [91, 87, 8, 23, 39, 8] and their references). However, in contrast to cost analysis, these and related methods do not infer cost functions on input data sizes but rather absolute maximum execution times, and they generally require the manual annotation of loops to express an upper-bound on the number of iterations. A first attempt to combine dependency of WCET and data size for PIC programs was reported in [34].

Energy analysis. Formal models of energy usage are not so well-developed compared with timing models, especially in high-level languages. Some work has been performed for the energy consumption of Java Bytecode programs, based on a simple low-level model of the energy consumed by the execution of each Java Bytecode. The analysis techniques are similar to those for complexity analysis. Relevant work includes [65, 66, 64, 48].

Other approaches have been developed for estimating the energy consumption of programs (e.g. [83, 48]) based on measuring actual consumption at run-time for large sets of random inputs. This approach has the limitation that it applies only to the class of programs that have been measured.

Energy analysis of parallel programs. The energy analysis of parallel programs is of particular interest, since the widespread use of multi-core processors is partly driven by the need to control the energy-performance trade-off. Korthikanti et al. present in [46] an analysis of the energy consumption of a number of particular parallel algorithms executed on shared memory multi-core processors, which is used to establish the optimal number of cores to minimize the energy consumed by a given algorithm for a specific problem size while satisfying a given performance requirement. The analysis is not automatic, and it is a challenge to develop automatic analyses. In [45, 44], the authors argue that examining the relation between the performance of parallel algorithms and their energy requirements on multi-core processors may be facilitated by analyzing some scalability metrics. For a given problem instance (i.e., the execution of a given algorithm for a given input size), and a fixed performance requirement, energy scalability under iso-performance provides the optimal number of cores required to minimize the energy consumption.

Energy analysis of precision. The precision of computations is a highly relevant factor when considering energy optimizations that trade energy for precision. Floating point computations break most algebraic properties of numbers (such as associativity or commutativity), and introduce rounding errors at each step of the computation. This introduces problems for program analysis. Precision analysis must take into account the floating point computation norm [40]. Some analysis by abstract interpretation can take such rounding errors into account [15], but the rounding error is always assumed to be a worst case, and although the analysis is quite efficient, it only gives bounds on the output, not the imprecision of the computation. Other analyzers based on abstract interpretation [30, 60] give sound bounds on the difference between an idealized computation using real numbers and the actual floating point computation. It is even possible to compute program transformations to improve the precision with respect to the real number semantics [59].

Other analyses. Other resources relevant to energy consumption will be considered. A general framework for analysis of user-defined resources is defined in [66]. It infers platform-dependent resources by including a one-time profiling phase of a given platform in order to determine the values of certain parameters for that platform. The framework has also been particularized to the estimation of execution times in [62, 61]. The approach in [61] is applicable to programs running on a bytecode-based abstract machine.

Static analysis for energy use can be directed also at subsidiary properties that are critical for understanding resource use in a program. Examples of such properties are patterns of use of shared

resources such as memory and communication channels, and the use of energy-expensive operations such as communication. This is a relatively unexplored area for static analysis; a recent relevant work is [58].

**Energy modelling at low and high level** Energy models will form the basis of energy analysis techniques and will allow energy use of a program to be estimated without necessarily running it on existing hardware.

Low-level modelling of energy. Estimated energy use of a design can be obtained based on simulating its netlist using the program as simulation stimulus (test vector). The low-level energy model underlying such simulations are toggle counts that can then be characterized with respect to energy consumption based on the fabrication process data provided by the chip manufacturer (this typically is closely protected Intellectual Property). While the latter approach does not require the hardware to be manufactured, allowing energy consumption values to be obtained early in the system development process, the associated simulations are computationally extremely expensive. For example, simulating 10M cycles on a 10M gate design can easily take a week (if not two) even if running on a huge server farm. Significant reductions, from weeks to hours, can be obtained using expensive dedicated emulation hardware.

Various approaches have been developed to establish power dissipation models for hardware at abstraction levels above netlist. Typical examples include models at the micro architectural cycle-accurate level [11] and the instruction level [88]. The latter links the software to the hardware as the Instruction Set Architecture (ISA) is the target of the compilation process, which translates a source code program into an executable sequence of instructions, also referred to as assembler code. For software this is typically the "lowest" level of abstraction, while for hardware design this is a "high" level of abstraction. In fact, the ISA serves as the functional specification in the hardware design process.

Higher-level energy modelling. More recent approaches [71] promote using several levels of abstraction, effectively providing multi-granularity models which offer designers a choice in trading off accuracy versus simulation speed. These models most typically are integrated into the design-flow in order to speed up simulation time with reasonable success. However, formal analysis of such higher-level models, used instead of simulation, can completely eliminate or more significantly reduce effort currently invested into simulation. It should be noticed that in reality, the base cost of an instruction can vary depending on the value of operands and, more generally, depending on the state of the processor at the time the instruction is executed (the execution history). Further work on incorporating such dependencies into the model are required.

Assertion language integrating analysis and modelling Energy models must be given a suitable representation within analysis algorithms. Models can take many forms, from simple lists associating instructions with a fixed energy cost, to functions applied to a whole section of code and taking various parameters expressing input data and execution environment.

At the same time, results derived by analysis have to be represented in a form both suitable for manipulation in the analysis algorithm and for interpretation by the user. Information on energy usage derived by analysis can also be compared with user-supplied assertions, and thus the results should be in a form readable by designers.

This takes the form of an assertion language that binds together models, analysis results, and user assertions.

Various available assertion formats. For hardware design, where power has long replaced performance as a prime design goal, the Common Power Format [84] provides hardware designers with a file format

to specify power-saving features of the design. These specifications are then used by synthesis and verification tools. This permits hardware designers to express the design intent with respect to power saving at design time. The use of assertions to express functional hardware properties to be verified either formally or during simulation is now standard practice in industry [25].

At the software level, assertion languages to express program properties to be checked statically or at runtime have been proposed for several declarative and object-oriented programming languages (e.g., Eiffel [63], Racket [24] and Ciao [35]). Assertions allow the users to express contracts between program components, typically talking about functional properties, and are the basis for the so called "design by contract" method [63]. The use of a multi-purpose common assertion language for integrated program verification, analysis and optimization has been proposed in the context of a multi-paradigm (declarative) language [35], which also allows to express some non-functional properties.

Currently, such languages do not permit non-functional properties, such as timing and energy budgets, to be integrated into the code from the outset. That is why, for software, timing and energy are a consequence of the design rather than a design goal. XC [89], the language designed to best utilize the features of the XMOS XCore processor, provides a mechanism via pragmas for programmers to annotate code with timing requirements, which can then be checked for single threaded programs only using the XMOS Timing Analyzer [93].

To lift timing and energy requirements to first class design goals for software development, a suitable assertion language must provide programmers with expressive constructs to specify these constraints at the same time as the code is being developed: this language must be integrated with the language in which energy models and analysis results are represented.

# B1.3.3 What optimizations are enabled by energy transparency?

Program transformations are studied in many contexts. In this project the aim is to optimize with respect to energy consumption. In general the task is twofold: firstly to recognize the opportunity for a transformation, namely the semantic conditions that allow one piece of code to be replaced by another, and secondly the selection or generation of the new code that replaces the old, reducing energy consumption.

The analyses discussed above will be used to identify opportunities for optimizing transformations. Typically the conditions are obtained from a global analysis, establishing that some condition holds in all (a possibly unbounded number) of possible executions of code.

Program Specialization and Partial Evaluation. In many applications, especially when code is developed in high-level languages or from library modules, code is executed only in a restricted context, with constraints arising implicitly from the initial state and the call structure of the program. Detecting such constraints is in general a non-trivial task requiring a global analysis to propagate the effects of input restrictions through the program. Specialization of code with respect to constraints can enable redundancies to be removed, with considerable savings of time and energy.

Partial evaluation and related specialization techniques using statically known input have been researched since the 1970s and numerous tools have been developed for a variety of programming languages. A bibliography of applications can be found at http://readscheme.org/partial-eval/. In particular, tools have been developed for imperative and object-oriented languages [27, 14, 82], for logic languages [52, 70] and for functional languages [33, 42, 13]. Frameworks integrating specialization with program analysis have been defined [74, 50], and program analyses aimed at improving specialization have also been developed, e.g. [26].

Specialization of interpreters. Recent work in both analysis and specialization makes use of metalanguage reflection, allowing an analyser/specializer for one language M (the metalanguage) to be applied

to programs in another language L (the target language). This approach has been used for example for partial evaluation of Java bytecode [29] and PIC assembly code [34] both of which used a partial evaluator for constraint logic programs. It has also been applied for analysis of high-level specifications in Petri nets [53] and analysis of linear hybrid automata [6]. It is now also well understood how to obtain optimal specialization of interpreters [51, 7]. It is expected that this interpretation technique will be adapted in the project for handling higher-level languages and execution strategies.

Local optimizations. A useful class of optimizations, that is common in low-level but not high-level code, is the replacement of some code by equivalent code that is more power-efficient. At the machine level, lookup tables typically record short sequences of assembly language instructions that can be replaced by equivalent more efficient sequences. These ideas could be extended to high-level code, where individual or sequences of library function calls could be replaced. Such tables can also be accumulated by a programming environment, to save inferring the same optimizations many times.

Parallelism - transformations and analyses. The exploitation of parallelism to reduce energy consumption is receiving increasing attention and will be researched in the project. The general idea is to split sequential tasks into independent subtasks that can be executed by different cores running at a lower frequency, yielding lower net energy use for the same task. For example, the energy consumption analysis proposed by Korthikanti et al. [46, 45, 44] can be used to determine the optimal number of cores to minimize the energy consumed.

It is important to ensure (functional) correctness of parallel execution (in the sense that the parallel program must behave the same as the corresponding sequential program) [12, 36]. This is often a matter of proving the independence of the subtasks using static analysis. It is also necessary to ensure (practical) efficiency [57, 56]. For the latter, we must take into account the overhead associated to parallel execution (e.g., due to communication, or parallel task creation) and the one associated to changing clock frequency in order to ensure that such costs do not exceed the benefits of parallel execution.

Trading off Quality-of-Service against energy Optimizations that save energy, while possibly losing precision, performance or some other quality-of-service measure will be studied. Some techniques from the literature exist and will form the basis of research in the project, augmented by energy analyses. PowerDial [37] is a state-of-the-art *autotuner* that converts static configuration parameters that already exist in a program into dynamic "knobs" that can be tuned at run-time. This technique is automatic but requires the user to provide training data, an output abstraction and identify a set of parameters (static configuration parameters) in the program.

Other approaches use program transformations that indirectly and dynamically reduce energy consumption. Hoffmann et al. proposed SpeedPress, a framework designed for exploiting performance-accuracy trade-offs using a technique called loop perforation [79, 80, 81]. Loop perforation transforms the program loops to execute only a subset of the iterations in the original computation. This technique is automatic but requires the user to provide training data, an output abstraction and bounds on output distortion.

Similarly, a number of other mechanisms have been developed for dynamically varying application behaviour to maximize performance subject to an accuracy constraint or vice versa. Specific mechanisms include multiple selectable implementations of a given component or components [4, 5, 95]; sampling inputs to reductions [95], skipping tasks in parallel programs [75, 76]; approximate function memoization (returning a previously computed value when the arguments of the new function call are close to the arguments of the previous function call) [77]; and approximate data types (data types that return approximate results for operations) [78].

# Power/Energy management at OS level(DVFS) with scheduling policies

At the level of the Operating System (OS), energy efficiency techniques based on *dynamic voltage and* frequency scaling (DVFS) have been explored in the research community [3, 85, 90].

In [90], models were developed based on parameters such as memory requests per cycle and instructions per cycle, which can be counted using the performance-monitoring unit (PMU) available in most processors. By predicting a workload's response to a change in frequency, a more energy-efficient frequency can be chosen at each scheduler invocation. Snowdon [85] enhanced this approach by developing a technique to choose automatically the best model parameters from the hundreds of possible events that modern PMUs can measure. His framework uses predictive models for execution time and power consumption. These provide an estimate of the energy consumed by the CPU when executing a task. Choosing parameters and their coefficients requires a one-time model-characterization on the system that is being modelled.

In [3], the optimal frequency selection is considered on multicore processors in the presense of resource contention, since cores of a chip share resources such as caches and memory interfaces. Combining tasks that run best at a certain frequency does not pay off if it leads to resource contention. The work analyzed scheduling for avoiding resource contention and for optimal frequency selection. It argues that the two are opposing goals, and that scheduling to avoid resource contention is crucial both in terms of performance and energy efficiency. This work proposes scheduling policies, using activity vectors for representing resource utilization, that reduce contention significantly by co-scheduling tasks with complementary demands.

# B1.3.4 What are the implications for tools and methods?

**Verification** Verification is the process used to demonstrate the correctness of a design with respect to the requirements and specification. Traditionally, verification has concentrated on establishing functional correctness. In the hardware community, the scope of verification has recently been extended to include non-functional properties, i.e. verifying that a design satisfies specification constraints beyond functional correctness, such as low-power features [84].

Verification of energy-related properties. Energy transparency opens up the possibility of tools that allow the software engineer to verify assertions about energy usage. Verification based on static analysis, particularly techniques based on abstract interpretation, consists essentially of comparing derived properties against specified or desired properties. Even though static analysis in general derives safe (over-) approximations of program behaviour, many typical properties, especially safety properties, can be proved. Most work on verification based on static analysis focusses on the proving of conformance to functional properties and typically results in the outcome true/false/unknown. However, in the case of properties such as resource usage, it is necessary to extend analysis to produce results which include properties such as upper- and lower-bounds on execution time and usage of energy, memory, or other types of resources. For example, it may be possible to say that a certain result holds if the input data size is in a given range.

The consortium has experience in the development of state-of-the-art frameworks for (static) verification of general resource usage program properties, based on static analysis [55, 35, 10]. Although initial results in this topic are quite promising, there are however open challenges that remain to be solved, as for example, dealing with richer resource-usage requirements (and hence analysis), and techniques for comparing analysis information against specifications in order to prove them.

A related problem is debugging of energy-related "bugs". Some previous work on debugging of resource usage properties exists [72, 35] and will be extended in the project.

Energy as a first-class design goal. There is already evidence that energy usage is becoming a major software design goal in some areas (see for example articles in the ISLPED conference series http://www.islped.org/). The areas in which some success has been achieved are either where design is close to hardware, such as embedded systems, or where there are very specific use-cases and computation patterns, as in data-centres.

Energy transparency will enable us to extend the range of applications in which energy is a first-class design goal. Progress will depend on the precision and scalability of energy analyses, and on the quality of the energy models available.

#### B1.3.5 Further research beyond the project

The project is expected to establish the feasibility of energy transparency, implement prototype tools and investigate the optimizations enabled on a range of case studies. Many areas of future work will still exist. Among these are:

- Hardware design for energy transparency. How to design hardware to facilitate analysis of energy usage and hence energy transparency.

- Deeper transformations and optimizations. As multicore processors proliferate the problem of automatic parallelization will become more urgent in order to achieve potential energy savings. Although this project will investigate some parallelizing transformations, many more challenges will remain.

#### B1.3.6 Project Strategy and Research Areas

The preceding discussion identified key areas of research relevant to achieving and exploiting energy transparency. The following summary outlines the approach to a number of research problems to be taken in the project, and the associated work packages.

XCore architecture. Many techniques researched in the project will be processor-independent, but in some cases we need to restrict ourselves to a single architecture, for example when modelling an ISA. We have chosen to use an XMOS XCore for those experiments because it is a scalable multicore, can run different cores at different speeds, and is event-driven at architecture-level, enabling power-efficient implementations.

- Energy Modelling (Low level): Work Package 2. ISA-level models will be established for the XCore, initially associating instructions with average values. A significant advancement of the state of the art with respect to modelling will take advantage of the fact that formal analysis can also be performed on the basis of cost functions, rather than just cost values. Such cost functions can capture dependencies that influence the energy consumption of an instruction (such as operand values or execution history). The consortium has expertise in formal modelling and verification of designs, including designs of industrial complexity, at different levels of abstraction [94, 92, 43, 21, 41, 38].

- Energy Modelling (High level): Work Package 2. The modelling of energy usage at higher levels goes beyond the state of the art, and will be achieved using semantic mapping techniques on the one hand and dynamic profiling on the other. Explicit interpretive models of higher-level languages and execution models (including parallelism) will be used to lift low-level energy models to more abstract structures.

- Common Assertion Language: Work Package 2. The project will advance the state of the art by defining a common assertion language for expressing energy and timing properties in languages used by the embedded software design community. In particular, this language will allow the expression complex specifications including energy consumption functions which depend on data properties (such as data size), other environmental properties (such as clock frequency and voltage) and inter-module contracts. The assertion language will be multi-purpose, used for analysis, optimization, and verification and debugging of embedded systems, allowing (energy) information flow between different components of the integrated tool set.

- Energy analysis: Work Package 3. We will focus on the continued adaptation of advanced cost and WCET analysis techniques to energy use, and on development of techniques for inferring upper- and lower-bounds on energy use. Furthermore, we will integrate timing analysis for parallel programs with energy use analyses to derive energy use for multi-core applications. Existing and new techniques for energy analysis will be applied to the main target languages used in the proof-of-concept for the project, namely, the XC language and XCore assembler. Our research will make advances in integrating analysis of energy use in parallel programs with analysis of access of shared resources. All three aspects will also advance the state of the art in identification and classification of applications with respect to scalability of analysis.

- Verification and debugging of energy properties: Work Package 3. Our work on verification focuses on developing novel automatic verification and debugging techniques and tools based on static analysis that support rich specifications about energy usage (as well as timing and precision) properties of programs, and apply them to industrial languages. We will focus on static verification, and will produce novel techniques for the comparison of analysis information against specifications involving energy, timing and precision properties. To complement verification, we will produce novel techniques for debugging the energy usage of programs.

- Program transformations: Work Package 4. In the project we will further develop resource-aware specialization in general and energy-aware partial evaluation in particular. In particular for energy-aware specialization, new empirical insights will be gained and new techniques developed. These techniques will further tighten the link between abstract interpretation and program specialization. We will also explore parallelization techniques to automatically derive energy efficient parallel versions, while giving support to the integration of both, manual and automatic techniques. The analysis results of parallel programs will be applied to exploit XC and XCore language features to parallelize code.

- Dynamic program optimizations: Work Package 4. Energy transparency will allow a radical re-interpretation and extension of techniques available in the literature, such as the techniques discussed earlier for trading off energy usage against precision or speed of computation, and run-time scheduling which takes account of global energy consumption of a set of energy-consuming tasks. We will explore integration of dynamic transformations such as autotuning and code perforation with advanced energy models developed in Work Package 2.

- Benchmarking and Optimality: Work Package 5. A new notion of optimality will be defined and explored, based on the idea of the minimal energy achievable by optimal utilization of existing hardware. This will provide a pragmatic and realistic approach to benchmarking and is adaptable to all platforms.

# B1.3.7 Related Projects

ASAP: Advanced Specialization and Analysis for Pervasive Computing (2002-2005) was an EU FP5 FET project (38059) to automate as much as possible the development of sophisticated

and reliable software for pervasive computing platforms using high-level languages and analysis, verification, and specialization techniques. The results included a novel toolkit based on the ideas above available as open-source code. Partners included the precursor to IMDEA, University of Bristol, HHU Düsseldorf and the University of Roskilde.

**SAFT: Static Analysis with Finite Tree Automata**. 2007-2010. Funded by Dansk Forskningsråd for Natur og Univers (FNU = Danish Natural Science Research Council) under grant FNU-272-06-0574. Partner: RUC.

MERIT/COMVERS: Resource-Aware and Verifiable Mobile Computing. 2005-2009. Funded by the Spanish Ministry of Science and Education (MEC) under grant TIN2005-09207-C03-01. Partner: IMDEA.

ES\_PASS: Embedded Software Product-based ASSurance. 2007-2009. EU ITEA2 cluster of EUREKA Program, Project number 06042, Spanish PROFIT grant FIT-340005-2007-14. Partner: IMDEA.

**DOVES: Development Of Verifiable and Efficient Software**. 2009-2013. Funded by the Spanish Ministry of Science and Innovation (MICINN) under grant 2008-05624/TIN. Partner: IMDEA.

Numeric and Symbolic Abstractions for Software Model Checking. 2011-2013. Funded by Dansk Forskningsråd for Natur og Univers (FNU = Danish Natural Science Research Council) under grant FNU-10-084290. Partner: RUC.

Formal Modelling and Analysis of the XCore Instruction Set Architecture Design. 2010-2011. Funded by the Knowledge Transfer Secondment Scheme of the UK Engineering and Physical Sciences Research Council under grant number EP/H500316/1. Partner: UNIVBRIS and XMOS.

Understanding the State of the Art in Power-Aware System Design. 2010-2011. Funded by the Royal Academy of Engineering under agreement number 10465/258. Partner: UNIVBRIS and XMOS.

#### B1.4 S/T Methodology and Associated Work Plan

#### B1.4.1 Overall strategy and general description

ENTRA aims to make energy usage transparent throughout a system, promoting energy efficiency to a first-class goal in design and system management.

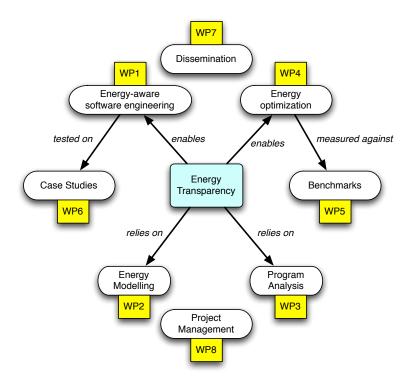

The project strategy can be visualized as in Figure 2. The central project goal of *energy transparency* relies on scientific advances in two main areas: modelling of energy usage from silicon through to high-level language constructs (WP2: Energy Modelling Through the System Layers) and program analysis, both static and dynamic (WP3: Analysis and Verification).

Achieving the goal of energy transparency enables the project to study novel program optimizations that reduce energy usage at both design-time and run-time (WP4: Optimization) and to investigate how energy transparency in tools and methods enables energy-aware software engineering (WP1: Energy-Aware Software Engineering).

Benchmarking suites (WP5: Establishing the Benchmarks) and design case studies (WP6: Evaluation) will be developed in the project to support the optimization and evaluate the software engineering work packages respectively. Finally, WP7 (Dissemination, Collaboration and Exploitation) covers the consideration of how to present the project results to a wider audience and initiate follow-up activities, and WP8 (Management) covers project management.

Figure 2: ENTRA Work Packages

**Project Stages** The project strategy is to follow four stages that successively integrate the fundamental components of energy transparency. A complete list of milestones, including those concerned with Management and Dissemination, can be found in Part A. Some additional description is added below, explaining how it is established that each (technical/scientific) milestone has been reached. The deliverables are described in the list of deliverables of Part A.

- 1. Define a common assertion language that integrates the fundamental components of energy transparency, namely program analysis, energy models and the software engineer's view of the energy usage of a program. This stage concludes with **Milestone 1** at Month 12. This milestone will be established by scenarios showing the use of the assertion language described in Deliverables D2.1 and D3.1, in which energy models and analysis results are expressed in the common assertion language.

- 2. Energy modelling and program analysis tools will be integrated, leading to a first energy analysis prototype. This stage concludes with **Milestone 2** at Month 18. This milestone will be reached when the lower layer energy models of WP2 are connected to the higher layer analysis of WP3, and the first energy consumption estimations for XC programs are inferred (Deliverables D2.2 and D3.2).

- 3. Optimization prototype tools will be applied based on the energy analysis, and results compared with idealized benchmark optimizations. This stage concludes with **Milestone 3** at Month 24. This milestone will be established at a project working meeting where a prototype optimization tool will be demonstrated on at least one of the project case studies.

- 4. The initial experiments and prototype tools will be extended, results evaluated, and advanced topics such as energy contract verification and dynamic scheduling will be investigated. This stage concludes at **project completion** at Month 36.

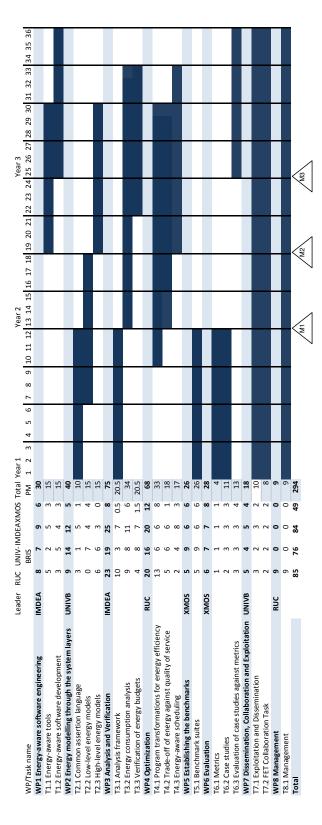

The work packages have been identified to address the specific objectives to be achieved by the ENTRA project. Individual work package effort allocation is based on a cooperative estimate of the needed person months, jointly made by the consortium members during project preparation and based on their practical experience from collaborations in previous joint projects. Every work package has a work package leader who will be responsible for the work package progress, deliverables and milestones. The work package leader reports to the project coordinator. Work package leaders have been nominated according to skills and experience of partners. Each task is labelled with the participating project partners. The heaviest work packages in terms of effort are WP3: Analysis and Verification and WP4: Optimization, since these require significant advances over the state of the art.

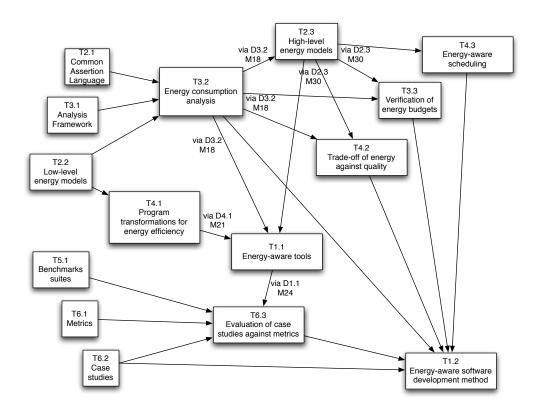

**Dependencies** Figure 3 shows the key task dependencies. These tasks are described in the work package description table of Part A, and their timing is given in Section B1.4.2. In some cases the dependency links are labelled by a deliverable, in particular where the dependent task receives input from an ongoing preceding task via some intermediate report or prototype. Apart from the defined dependencies, regular communication will ensure flow of ideas and feedback from one WP to another. The consortium is small and cohesive, and the project team leaders will foster a culture of communication and collaboration, leading to greater exchange of ideas and progress reports, especially at quarterly project meetings. In particular, tasks in WP2, WP3 and WP4 will continuously obtain feedback from each other.

Figure 3: Dependencies

**Risks and contingencies** Risks can be classified into technical risks and organisational/commercial risks. Risk management of the project is based on assessing the risks and planning preventative actions (actions taken a priori to reduce the chance of a risk happening) and ameliorating actions (actions to be taken if a risk does occur to reduce its effect).

Technical risk is part of the nature of adventurous and innovative research. Organizational risk is inherently present in projects that involve international collaboration. The strategy in ENTRA is to reduce the likelihood of a risk occurring and to put measures in place to significantly limit the impact of the risk in the unlikely event that it does occur.

The following sections list the technical and organizational risks identified by the ENTRA consortium together with the preventative/ameliorating actions planned.

#### **Technical Risks**

- Risk of not meeting the milestones: Risk is associated with not meeting the outputs specified for the 3 project milestones.

- Milestones have been placed strategically so that task outputs are available to reach the milestone. Partners are aware of the milestone objectives and of their importance to reach the next phase of the project. The work is structured in such a way that it permits alternative paths to reach technical objectives, this significantly reduces the risk of not meeting objectives.

- Risk of techniques and methods not being mature enough to be adaptable: ENTRA is primarily focused on providing proof of concept solutions and on assessing

viability. XMOS will assess the techniques and methods during the project, especially during evaluation and adapt what is deemed to be mature.

- Risk of techniques and methods not being mature enough to be integrated into a fully working prototype: There is a high technical risk that not all of the tools developed will be mature enough to fully integrate into the toolset at the end of the project. In this case, the prototype will be more limited in that the output of a phase may need manual processing before it is passed to the next phase. Thus the techniques and methods will still be demonstrated, but not as automatically (and hence user friendly) as ideally desirable.

- Risk of complexity and related scalability of models: There is a risk in the scalability of models single core models are low risk but multi-core models are a higher risk; having a progression from one to the other reduces the overall risks.

# Organisational etc. Risks

- Staff recruitment and associated delays in project start: There are a number of potential problems in recruiting staff especially in academic organisations. Academic organisations are frequently constrained by not being able to recruit until contracts are in place, which may lead to staff not being hired in time for the start of the project.

In ENTRA, a lower effort profile has intentionally been planned at the start for these partners for the first few months to allow for this, and thus avoid tasks, especially those

- Change of interests: There are always risks in partners changing their focus and the research no longer being aligned fully with their commercial interests.

In ENTRA we have reduced this as far as possible by having an industrial partner for whom the results of this project are a key to their core business offering.

with tight dependencies, starting late and causing project delays from early in the project.

- Failure to come to an Consortium Agreement: The partners may not reach consensus over the Consortium Agreement.

- This is a very small risk because several of the partners in ENTRA have previously worked together in collaborative projects. During proposal writing partners agreed on the DESCA FP7 consortium agreement as a basis. The actual agreement will be agreed upon and signed at the start of the project.

- Financial viability risk: A small risk is associated with partners not being able to finance their involvement.

- The academic partners are mature institutions and financially stable. XMOS has been in business for more than 7 years and is financially sound and in a position to cover its commitments in ENTRA.

# B1.4.2 Timing of work packages and their components

Figure 4: Gantt Chart including Work Packages, Tasks and Milestones

# **B2** Implementation

# **B2.1** Management Structure and Procedures

The general management of the project is based on the following principles:

- 1. Management should be consistent with the size of the project.

- 2. Decision making should be quick and simple, but respect all partners' interests.

- 3. Decision making should be by consensus as far as possible.

- 4. Where consensus cannot be reached, a simple process should be used.

A Consortium Agreement based on the DESCA FP7 model (http://www.desca-fp7.eu/) defines the details of the project management structure and procedures and the handling of financial matters. The main points from this agreement are summarised in this section but the Consortium Agreement is the definitive reference.

Management consists of the following formal "actors":

- The Project Coordinator (RUC).

- The Project Coordination Committee.

**Project Coordinator:** The Project Coordinator (RUC) (whose team leader is referred to as the Project Manager below) is responsible for the overall management and coordination of the entire research project. A special emphasis within its responsibilities is to ensure in cooperation with WP Leaders the overall integration of the individual WPs and also to chair the project board, the Project Coordination Committee. Furthermore, the Project Coordinator is the only official channel through which interaction with the European Commission takes place, especially with regard to the submission of deliverables, aspects related to third parties and the consortium.

**Project Coordination Committee:** The Project Coordination Committee (PCC) consists of one representative of each beneficiary. The PCC will meet at least once a year and at any time upon written request by one or more beneficiaries. The PCC is the highest decision board and its main task is project governance. It will have the overall responsibility for all technical, financial, legal, administrative, ethical, and dissemination issues of the project. For this reason, the PCC will monitor and assess the actual progress of the project and make amendments if necessary.

In particular the PCC will be responsible for the following tasks:

- Content, finances and intellectual property rights

- Proposals for changes to Annex I of the EC-GA to be agreed by the European Commission;

- Changes to the Consortium Plan (including the Consortium Budget);

- Changes to the definition of and access rights to Background.

- Evolution of the Consortium

- Entry or withdrawal of parties to or from the Consortium and approval of the conditions for such changes;

- Declaration of a Party to be a Defaulting Party and consequent measures to be taken;

- Proposal to the European Commission for a change of the Coordinator;

- Proposal to the European Commission for suspension of all or part of the Project;

- Proposal to the European Commission for termination of the Project and the Consortium Agreement.

**Voting Rules and Quorum:** Decisions of the PCC require the presence or representation of two-thirds (2/3) of its Members. Each Member shall have one vote. Defaulting Parties may not vote. Decisions shall be taken by a majority of two-thirds (2/3) of the votes.

Responsibilities of Beneficiaries: Each beneficiary will nominate a local team leader who will be responsible for the planning, execution and controlling of that beneficiary's activities in the project, in compliance with the decisions of the PCC. The beneficiary team leader's responsibilities are:

- Provision of interim reports on project resource usage every six months to the Coordinator;

- Administration and scientific coordination activities;

- Implementation of all beneficiary action plans;

- Developing and maintaining a culture of communication and reporting among the team members;

- Creation of efficient team structures to minimize the number of meetings while being flexible.

# **Project Meetings**

The project has planned for at least one physical meeting per year. The timing of these will vary slightly according to the work plan, so that they can be aligned with the best points for the collaboration between tasks.

In addition, teleconference calls or online meetings every four months will ensure that progress is tracked and any issues are picked up quickly and dealt with at the earliest possible opportunity.

Where possible, meetings will be arranged alongside existing meetings and conferences to minimise costs and travel time.

#### Conflict Resolution will follow the following procedure:

Stage 1 - this is an informal stage where the Project Coordinator will discuss individually with the parties and together with the parties to determine the precise nature of the conflict and explore possible solutions to the conflict.

If the conflict cannot be resolved, then the process is to go to the next stage.

Stage 2 - this is a formal stage. The parties will bring the conflict to the Project Coordination Committee, which is the formal decision making body in the project.

If the PCC cannot resolve the conflict to the satisfaction of the parties, then the process is to go to the next (and final) stage.

Stage 3 - this is the external stage. The conflict will now be resolved according to the Consortium Agreement, which will include an option of arbitration.

<u>Project Coordinator</u> The Project Coordinator will be John Gallagher, who has over 20 years' experience of European collaborative research projects, and has worked in both academic and industrial institutions. He has been the team leader in 6 European projects. He will be assisted by administrative project manager Dixi Louise Strand.

# Project Work Package Leaders

The following are the assigned work package leaders:

| Work Package                                      | Leader          |

|---------------------------------------------------|-----------------|

| WP1 Energy-Aware Software Engineering             | P. López-Garcia |

| WP2 Energy Modelling Through the System Layers    | K. Eder         |

| WP3 Analysis and Verification                     | P. López-Garcia |

| WP4 Optimization                                  | J. Gallagher    |

| WP5 Establishing the Benchmarks                   | H. Muller       |

| WP6 Evaluation                                    | H. Muller       |

| WP7 Dissemination, Collaboration and Exploitation | K. Eder         |

| WP8 Management                                    | J. Gallagher    |

# Quality Assurance

Quality assurance is simple and will consist of peer review of technical deliverables for accuracy and conformity with the project workplan. The Project Manager will be responsible for ensuring the timely delivery of deliverables to the EC and the external reviewers.

# **Publication Vetting**

The Project Manager will vet all material intended for publication to check that none of it is prejudicial to the industrial beneficiary's needs to protect intellectual property as a precautionary measure.

In cases where a potential risk is found, the Project Manager will chair discussions with the beneficiaries involved to resolve it by changes to the material or an agreed reasonable delay to allow IP protection e.g. patents to be filed without prejudice. If resolution is not possible informally, then the normal dispute resolution procedure will be followed.

#### Risk Management

The project manager will keep a risk register updated every quarter. In addition, the project manager will keep a watching brief on industry developments that may affect the project exploitation. Both of these will be reported on in the management reports.

# **B2.2** Beneficiaries

# B2.2.1 Roskilde University

Roskilde University (RUC)) is a Danish state university founded in 1972 with the objective of providing research and education at the highest level in the fields of natural science, social science and the humanities. Activities at Roskilde University are organised in six departments (institutes) and degrees are offered in a wide range of subjects at Bachelor, Master and Ph.D. levels. The University is the daily place of work for around 8000 students, 700 researchers and lecturers as well as 250 technical/administrative staff. Classical thoroughness combined with problem-oriented interdisciplinary approaches characterizes research at Roskilde University. The Department of Communication, Business and Information Technologies (CBIT) is an innovative and interdisciplinary university environment with over 100 academic staff. CBIT combines information technology, the social sciences and humanities in the study of the interplay between communication, business and information technology in theory and in practice. CBIT contains seven research groups including the "Programming, Logic and Intelligent Systems" group (PLIS). The PLIS group (http://plis.ruc.dk) contains 7 full-time researchers plus a number of PhD students and postdocs. The group investigates foundations, tools and

languages for the development of adaptable, reliable, human-oriented computer systems. The group's research covers theoretical foundations, languages, tools and semantic models together with application areas. The main research topics are: Programming languages and tools; Knowledge-based systems and intelligent interaction with systems; Logic and knowledge representation. Expertise and Related Activities The group is active in topics around static analysis of programs and verification. Recent and current relevant projects carried out within the PLIS group include "ASAP: Advanced Specialization and Analysis for Pervasive Systems," funded by the EU Framework 5 programme, 2002-2006; "SAFT: Static Analysis with Finite Tree Automata;" funded by the Danish Natural Science Research Council, 2007-2010 and "Numeric and Symbolic Abstractions in Software Model Checking," funded by the Danish Natural Science Research Council, 2011-2013. The PLIS group has built up tools and expertise in program analysis and specialisation tools, including the CHA and Tattoo online tools (http://saft.ruc.dk/CHA, http://saft.ruc.dk/Tattoo) for numeric and symbolic analysis of constraint logic programs. These have been used previously for analysis of microprocessor code and real-time controllers. The group has expertise in integrating state-of-the-art solver libraries (SAT, SMT, BDD, polyhedra, octagons, etc.) into program analysis tools.

# Key personnel:

John Gallagher (leader of Roskilde project team). Professor in Computer Science. From 1990 to 2002, he was lecturer and then senior lecturer at the Roskilde University, UK. He obtained his PhD in 1983 in Trinity College Dublin and has had research positions at the Weizmann Institute, Israel, Katholieke Universiteit Leuven, Belgium and in industry in Germany. He has been active in the area of logic in programming, knowledge representations, program analysis and software development tools for 20 years, and has over 50 peer-reviewed papers in this area, particularly on analysis and specialization of constraint logic programs. He is in the steering committee of the ACM PEPM conference series, the executive committee of the Association of Logic Programming and is an Area Editorial for the Journal of the Theory and Practice of Logic Programming.

John will coordinate the whole project, as well as coordinating WP4. He will work mainly in WP1, WP3 and WP4 and co-supervise PhD students and research assistants hired in the project.

Mads Rosendahl. Associate Professor. Research topics include abstract interpretation, complexity analysis, set constraints and program specialisation.

Mads will contribute mainly to WP3, and will co-supervise PhD students and assistants working in WP1 and WP4.

Morten Rhiger. Associate Professor. Research topics include programming language implementations, including interpreters, compilers, and run-time code generation; type systems and type safety; multi-stage programming; denotational, operational, and monadic semantics; functional and other higher-order programming languages.

Morten will contribute mainly to WP1 and will co-supervise PhD students and assistants working in other WPs.

**Dixi Louise Strand**. Special advisor. She obtained her PhD from Computer Science, Roskilde University in 2003. Dixi has experience as the administrative research manager of a large collaborative project on innovation in virtual worlds funded by the Danish Strategic Research Council (2009-2011). Dixi has furthermore participated in two other strategic research projects, funded by the Danish Research Council, on IT design of web services (2000-2003) and IT-based collaboration in health care (2004-2007).

Dixi will assist the Project Coordinator and the Project Coordination Committee as project administration manager and will coordinate and contribute mainly to WP8.

# B2.2.2 University of Bristol

The University of Bristol (UNIVBRIS) is renowned internationally for its excellence in research across a wide range of disciplines, regularly being ranked amongst the top Universities in the world. It is a member of the Worldwide Universities Network and a member of the prestigious Russell Group of Universities in the UK. The Merchant Venturers School of Engineering (MVSE) at the University of Bristol has nine highly specialized Research Groups and several world-leading Research Centres. The research on Design Verification within the recently established Microelectronics Research Group concentrates on specification, verification and analysis techniques which allow designers to define a design and to verify/explore its behaviour in terms of functional correctness, performance, power consumption and energy efficiency. The University of Bristol was the first university in the UK to train Computer Science undergraduates in the skills expected from professional verification engineers. Research in the Microelectronics group is conducted in close collaboration with the local and international semiconductor design and EDA industry where group members have developed strong links to companies such as large multi-nationals including Infineon, ST Microelectronics, Broadcom, as well as Cadence and Mentor Graphics, and many smaller companies such as NVIDIA, Picochip, Xintronix and XMOS. Research and industrial collaboration in the MVSE are closely linked to teaching activities. The Department of Computer Science runs MEng/BSc and MSc programmes; most relevant to ENTRA are the MSc in Advanced Microelectronic Systems Engineering and also the undergraduate MEng in Computer Science and Electronics. The University of Bristol also hosts a world-leading Systems Centre where Sustainability is a major research topic.

# Key personnel:

Dr Kerstin Eder is Reader and Research Fellow in Computer Science. She holds a degree from the Technical University Dresden (Dipl.-Informatikerin) and an MSc in Artificial Intelligence from the University of Bristol. Her PhD focused on Computational Logic. Dr Eder's research activities are focused on Design Verification including both formal methods and simulation-based approaches. She has authored over 30 technical publications in fully refereed international conferences, workshops and journals and has been investigator on 7 externally funded research projects raising in excess of £1.8M in grant income. Her most recent projects are on formalizing processor instruction sets [92, 94] and on functional verification of adaptive robotics [31]. Since 2003 she has been advising the UK National Microelectronics Institute (NMI) where she is the lead academic in the NMI Design Verification Roadmapping initiative. Dr Eder initiated the introduction of the MSc in Advanced Microelectronics Systems Engineering at Bristol and has been Programme Director until 2010. In March 2007 she was awarded a prize for "Excellence in Engineering" by the Royal Academy of Engineering. Based on Dr Eder's expertise in Design Verification the University of Bristol was selected as a Lead University to head the Cadence Academic Network in the area of Advanced Verification Methodology. In October 2010 Dr Eder won a one-year Royal Academy of Engineering Industrial Secondment to XMOS with the aim to understand industrial power-efficient design methods. Dr Eder is an active member of the Systems Centre at the University of Bristol.

In January 2011 Dr Eder set up the Energy-Aware COmputing (EACO) Initiative<sup>1</sup> at Bristol. It brings together researchers and engineers with interests in energy-aware computing. EACO aims to go significantly beyond the state of the art by engaging both communities in collaborative research projects at the leading edge of science and technology. The EACO workshop series has attracted participation from leading industrialists and academics - locally, nationally and internationally. Dr Eder is now leading the EACO initiative toward the first set of collaborative research projects to be launched on 18 April 2012.

<sup>&</sup>lt;sup>1</sup>Further and up-to-date information on the EACO workshop series, the Industrial Partners and the latest news can be found online at http://www.cs.bris.ac.uk/Research/Micro/eaco.jsp.

Based on her profile and expertise both in energy modelling and verification, Dr Eder will coordinate the research in WP2 and the work in WP7. She will also contribute towards WP3, especially on verification, and participate in WP1 and WP4 tasks. Dr Eder will be the principal supervisor of the Research Assistants to be employed in Bristol during the project.

Dr Nunez-Yanez is a Senior Lecturer in Electronic Circuit Design. He obtained a BSc in Industrial Engineering and an MSc in Microelectronics Engineering from the University of La Coruna (Spain) and University Politecnica the Catalunya (UPC, Spain) respectively. He holds a PhD from Loughborough University. His expertise is in the area of reconfigurable computing using FPGAs, computer architecture and signal processing. During 2005 he was a Marie Curie Fellow at ST Microelectronics, Italy, investigating optimial couplings between a RISC processor and a dynamically reconfigurable fabric [68]. Dr Nunez-Yanez pioneered the area of lossless data compression using variable order Markov models in hardware to support optimal statistical compression of multimedia data without any loss of quality and real time processing [67]. In addition, he is active in the areas of high-performance reconfigurable computing and on-chip communication architectures exploring fault-tolerant computing paradigms. During 2011 he was an Industrial Fellow at ARM Ltd supported by the Royal Society, investigating techniques for high-level modelling and optimization of energy consumption in complex system-on-chips. He also continues work in efficient video/signal processing algorithms targeted to hardware architectures [69] and Bio-inspired computing [96].

Based on his profile and expertise, especially in high-level energy modelling, Dr Nunez-Yanez will contribute mainly towards the research in WP2 and WP5. Dr Nunez-Yanez will co-supervise the Research Assistants to be employed in Bristol during the project.

Dr Simon Hollis is a Lecturer in Computer Science. He holds an MA and a PhD in Computer Science from the University of Cambridge. His PhD focused on energy-saving interconnects, and his research interests range through computer architecture, novel clocking schemes, on-chip networks and parallel programming paradigms. In all his work, energy has been a primary focus, and has led to the creation of the energy-efficient 'RasP' and 'Skip-link' networks. He is currently building a communication-oriented 480 processor system, built on the XMOS platform. Dr Hollis has published 16 papers in internationally refereed conferences and journals, and teaches two undergraduate and post-graduate courses on embedded system and ISA design. He has hosted the UK Asynchronous Design Forum, dedicated to novel approaches to logic design.

Based on his profile and expertise, especially in computer architecture and parallel computing, Dr Hollis will contribute mainly towards the research in WP2, WP4 and WP6. He will also participate in WP3 tasks. Dr Hollis will co-supervise the Research Assistants to be employed in Bristol during the project.

Steve Kerrison holds an MEng Hons in Computer Systems Engineering. He received the Toshiba sponsored award for "Best Computer Systems Engineering Student" from the Department of Computer Science. His areas of interest are embedded systems development and computer architectures. He is now a PhD student with research interests in methods for energy-aware software implementations. During 2011 he has been working jointly with Dr Eder at XMOS to examine architectural and micro architectural features of processors that permit software control of power consumption for strictly-timed, real-time applications.

Steve will be contributing towards energy modelling in WP2, analysis in WP3 and benchmarking in WP5.

#### **B2.2.3** IMDEA Software Institute