# **ENTRA**

318337

**Whole-Systems ENergy TRAnsparency**

# Energy Optimization: Basic Static Techniques

Deliverable number: D4.1

Work package: Optimization (WP4)

Delivery date: 1 July 2014 (21 months)

Actual date: 22 August 2014

Nature: Report Dissemination level: PU

Lead beneficiary: Roskilde University

Partners contributed: Roskilde University, University of Bristol, IMDEA Software Insti-

tute, XMOS Limited

Project funded by the European Union under the Seventh Framework Programme, FP7-ICT-2011-8 FET Proactive call.

## **Short description:**

This deliverable describes the state of the art in the relevant energy optimization techniques together with a discussion of the optimizations to be applied to each case study.

The deliverable includes the following two attachments.

- D4.1.1. Study of Possible Static Power Reduction due to Temperature Hot Spot Reduction provided by Uniform Register Utilization. Technical Report.

- D4.1.2. From Relational Verification to SIMD Loop Synthesis. Published in the ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming, PPoPP '13.

## **Contents**

| 1 | Sum  | ımary     |                                                                  | 3  |

|---|------|-----------|------------------------------------------------------------------|----|

|   | 1.1  | Static    | Optimization Techniques                                          | 3  |

|   | 1.2  | Applic    | cation to the project Case Studies                               | 3  |

| 2 | Intr | oductio   | n                                                                | 4  |

| 3 | Clas | sificatio | on of Optimization Techniques                                    | 4  |

|   | 3.1  | Low-le    | evel Code Optimizations for Low Power                            | 4  |

|   |      | 3.1.1     | Power/Energy vs. Performance Optimizations                       | 5  |

|   |      | 3.1.2     | Thermal-Aware Compilation                                        | 7  |

|   |      | 3.1.3     | Register-file Energy Reduction                                   | 8  |

|   |      | 3.1.4     | Energy Efficient Compiler-based Task and/or Data Parallelization | 9  |

|   |      | 3.1.5     | Code Motion for Energy Optimization                              | 11 |

|   |      | 3.1.6     | Superoptimization                                                | 12 |

|   |      | 3.1.7     | Other Important Techniques                                       | 14 |

|   |      | 3.1.8     | Summary of Used Static Analysis Techniques                       | 14 |

|   |      | 3.1.9     | Concluding Remarks: Compiler Optimization Techniques             | 15 |

|   | 3.2  | Algori    | thm and Source-Code Energy-aware Optimizations                   | 15 |

|   |      | 3.2.1     | Re-computation vs. Communication                                 | 16 |

|   |      | 3.2.2     | Code Level Parallelization                                       | 16 |

|   |      | 3.2.3     | Precision (QoS) - Energy Trade-off                               | 17 |

|   |      | 3.2.4     | Summary of Used Static Analysis Techniques                       | 18 |

|   |      | 3.2.5     | Concluding Remarks: Source Code Energy Optimization              | 19 |

| 4 | Opt  | imizatio  | on in the Case Studies                                           | 19 |

|   | 4.1  | Archit    | ecture and considerations                                        | 19 |

|   |      | 4.1.1     | Thread parallelism                                               | 19 |

|   |      | 4.1.2     | I/O and computations                                             | 20 |

|   |      | 4.1.3     | Core parallelism                                                 | 21 |

|   | 4.2  | Econo     | mics of power optimizations                                      | 21 |

|   | 4.3  | Real-t    | ime audio processing                                             | 22 |

|   | 4.4  | Robot     | and motor control                                                | 23 |

|   | 4.5  | Real-ti   | ime networking                                                   | 25 |

| 5  | Asse  | Assessment and Relation to Future Tasks                                      |    |  |

|----|-------|------------------------------------------------------------------------------|----|--|

|    | 5.1   | Focus areas for future research on optimization (WP4)                        | 28 |  |

|    | 5.2   | Relation to Dynamic Optimization                                             | 29 |  |

|    | 5.3   | Relation to Energy-Aware Software Engineering                                | 29 |  |

| Αt | tachn | nents                                                                        | 38 |  |

|    | D4.1  | .1: Study of Possible Static Power Reduction due to Temperature Hot Spot Re- |    |  |

|    |       | duction provided by Uniform Register Utilization                             | 40 |  |

|    | D4.1  | 1.2: From Relational Verification to SIMD Loop Synthesis                     | 45 |  |

## 1 Summary

## 1.1 Static Optimization Techniques

This report is the first deliverable from work package WP4 (Optimization). The aim of this report is to identify and classify energy optimizations for code at various levels and the supporting analysis techniques needed to realize them. Tools for *energy transparency* enable a software developer to see how much energy an application uses and how the energy usage is distributed among the parts of the code. Work packages WP2 and WP3 focus on the fundamental modelling and analysis techniques needed to achieve energy transparency (see Deliverable D2.1 [EG13] and Deliverable D3.1 [LG13]). Given this information, the developer aims to apply optimizations to make the application more energy-efficient.

The report concerns only static optimization techniques, namely optimizations that are made by transforming the code or by fixing hardware parameters before execution. Dynamic optimizations, based on such things as run-time scheduling and dynamic modification of hardware parameters will be considered in deliverable D4.2.

A variety of tool support can be applied to achieve the required optimizations. In this report we consider optimizations independently of whether they are achieved by hand or with tool support, and we do not consider tool support in detail. The ENTRA project will develop prototype optimization tools, but we also note that energy transparency enables the developer to focus hand optimization efforts in the most effective way even if optimization tools are not available. Furthermore energy transparency assists the developer to evaluate the effectiveness of optimization, whether carried out by hand or with tool support.

## 1.2 Application to the project Case Studies

The survey of techniques considers a wide variety of hardware platforms, many of them beyond the scope of the current project. However, in Section 4 we perform a first assessment of the opportunities for optimization in the project case studies (work package WP6, deliverable D6.1). Our approach is as follows: we first outline the main architectural features of the target hardware platform for the ENTRA case studies. Secondly we summarize the context in which energy optimizations are performed, taking into account economic costs of development and manufacture. Following this we make a first assessment of the opportunities for optimization in the three case studies described in Deliverable D6.1 [Mul13]: real-time audio processing, robot and motor control and real-time networking.

## 2 Introduction

Given that software controls the way that the hardware consumes energy, it is clear that in order to minimize the total consumed energy of an application we need to design the software with energy consumption in mind. An estimate by Intel states that energy savings by a factor of 3 to 5 could be achieved using software optimizations alone [Edw11]. Correctly fitting software algorithms to the capabilities of the underlying hardware has been identified as the most important step in software design for low power, above all other power optimizations [RJ97]. The importance of exploiting parallelism is also identified, and has become of increasing significance as parallelization has become the dominant method of delivering higher performance.

To identify effective optimizations, all levels of the software stack need to be considered. Starting from algorithm and/or application specification, through the compiler which produces the low level code, down to operating system and machine code which controls hardware operation, these should be optimized in a way to minimize the total energy consumed. In this report we will discuss each of the mentioned levels in more detail.

The underlying hardware system also has to be taken into account, given that the optimization requirements are not always the same. For example, in battery powered embedded systems it might be important to reduce the *total* energy, and also the *peak power* since both have an effect on battery life. However, in large-scale general purpose systems the *average* computation power determines the amount of generated heat, and along with it the activity of cooling system, whose energy consumption can become significant. Thus, before starting the optimization, the optimizing problem and its objectives have to be clearly specified. We also consider various metrics for energy measurement [Mul13], covering various aspects of static and dynamic power (wattage) and total energy consumption. In the rest of the text, power and energy optimization will be treated as the same objective, given their close connection.

## 3 Classification of Optimization Techniques

## 3.1 Low-level Code Optimizations for Low Power

Research on power-aware compiler optimizations is not very extensive, mostly due to the lack of reliable and effective evaluation methods. There are methods that have been evaluated using physical measurements on a set of benchmarks, and also simulation based methods, but in general they were not considered to be sufficient proof of their practical utility. Thus, energy transparency is important in providing ways to evaluate optimization effects.

In this section we will first explain the difference between the compiler optimizations for

performance and the compiler optimizations for power and energy. After that we will present the most representative techniques divided into the following four groups:

- Thermal-aware compilation

- Register-file Energy Reduction

- Energy Efficient Compiler-based Task Parallelization

- Other important techniques that do not fall into any of the above groups

Finally, we will give a summary of the static analyses used in the cited techniques and draw the most important conclusions.

#### 3.1.1 Power/Energy vs. Performance Optimizations

It has been widely accepted that existing compiler optimizations for achieving higher performance also achieve lower energy consumption given that higher execution time usually means higher energy. This is true for some of them, such as dead code elimination, common subexpression elimination, and in general all those that decrease the amount of work to be performed.

In these techniques we can also include all the loop optimization techniques that exploit memory hierarchy [RJ97]. The idea of these techniques is to introduce more locality in data accesses in order to be able to use the data stored in the parts of memory hierarchy closer to the processor, i.e., register file and/or cache. In essence, accessing the parts of the memory which are smaller and closer to the chip reduces the effective switching capacitance, thus reducing the energy consumption. However, some of these techniques introduce additional computation, thus increasing processor energy. For example, some linear loop transformations can result in complex loop bounds and array subscript expressions. Similarly, loop tiling can impose extra branch control operations. On the other hand, loop unrolling is expected to decrease energy consumption, since it decreases the impact of the loop overhead and in this way the total number of instructions.

All of this has been confirmed in the work of Kandemir et al. [KVI02], which explores the effect of the above-mentioned loop optimization techniques on energy. In particular, they evaluate energy consumption of matrix multiplication code on different cache configurations with different loop optimization techniques. Their conclusion is that the effectiveness of each technique depends on cache configuration, but in general the decrease of energy consumption does not follow the decrease of cache misses due to the effect of introducing additional computation in the core. Thus, they advise the use of these techniques along with other optimizations in order

to achieve savings on global level. In this way, they were able to reduce energy consumption by 55%.

One possibility presented in the same work [KVI02] is to combine loop optimizations, in particular loop fission, with the possibilities offered by hardware, in this case the existence of different memory banks that have different power modes. Loop fission in essence transforms a nested loop that contains multiple statements into a set of nested loops, each containing a subset of the original statements. In this way, the amount of memory needed in each loop iteration is reduced, which provides the possibility to use lower number of memory banks, and put the ones that are not used in hibernation mode.

In a similar fashion, compilers can help the operating system to decide when to turn on a particular power saving mode by inferring the time during which particular modules are inactive, so they can be turned off. The main issue with turning off modules is that their re-activation takes a lot of time. However, if the operating system knows when a particular module is to be used, it can start its activation and deactivation in a timely manner. An example of this is presented in [HPH+02], where an average of 70% reduction of disk energy is achieved. Another example is given in [SCO+07], where the compiler is able to derive disk access patterns, provided that it is aware of the disk layout. Based on the compiler-predicted future idle and active periods of parallel disks, a proactive disk power management can be implemented. In order to achieve additional savings, this information can be used for code restructuring in a way such that the length of idle disk periods is increased, which leads to better exploitation of power-saving capabilities.

Something similar can be done for Dynamic Voltage and Frequency Scaling (DVFS). For example, the compiler can infer the parts of the code where the processor can be slowed down with negligible performance loss [HK03]. Another example is presented in [SKL01], where the compiler provides an estimation of the execution time of each block. Hence, the static analysis necessary in this case is timing analysis. Here it is assumed that the worst execution time is the time of the critical path. Thus, if a block that is supposed to be executed next does not belong to the critical path, the operating system can calculate the slack time, i.e., the time difference between the block to be executed and the corresponding one that belongs to the critical path, and change the voltage and/or frequency in such a way that the execution time of the current block is (at most) the same as the execution time of the critical one.

A fundamental difference between performance and power optimizations is the model and/or metrics used. In the case of performance, the optimizations of the critical path are usually considered, while the optimizations that do not belong to the critical path usually do not affect performance. However, in the case of the power, each activity contributes to power consumption. A clear example of this is given by speculative activities, e.g., prefetching, which are executed based on a belief of a future behaviour. If the assumptions turn out to be false, additional work

has to be performed to undo the effects of speculative activities. If the critical path is not affected, it is clear that it will not affect performance, but obviously it can increase energy consumption. In the general case, this increase would have to be compensated by the overall energy benefit in order to be effective for energy optimization.

#### 3.1.2 Thermal-Aware Compilation

In recent years a number of solutions for thermal aware compilation appeared aimed at reducing hot spots, i.e., the highest achievable temperature. In this way, it is possible to reduce static power consumption, given its super-linear temperature dependence and the fact that it is becoming an important part of power consumption, as well as energy spent on cooling in general purpose systems.

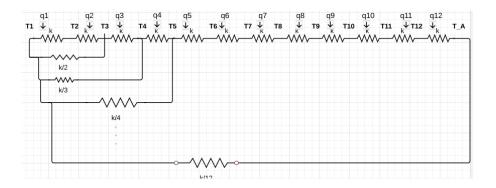

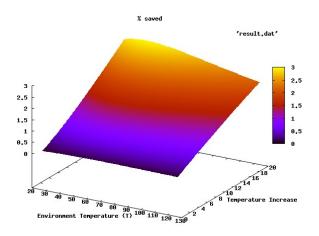

Researchers have identified the register file to be the hot spot of a processor, given its frequent usage and the way it is being accessed. Compilers usually assign a variable to the first free register, which means that the register located at the beginning of the register file will be used more frequently than the rest. For this reason, their temperature will be much higher than the temperature of the registers located further down the register file. In order to tackle this problem, the authors of the papers given in [AAB09, SAA10] propose to access the registers uniformly in order to avoid hot spot creation. This is usually performed by the compiler in an additional step called register re-assignment, using different techniques (heuristics mostly) to make the register usage more uniform. According to their results, hot spot temperature can be lowered by 11%. This can introduce significant reduction in cooling power in the case of general purpose systems. However, none of the papers give insight into static power reduction. We have performed some coarse grain estimations, according to which we could save up to 5% of static power with a register set of 12 registers in the cases of heavy register usage<sup>1</sup>. This means that these techniques cannot provide significant savings for embedded systems, and would be more appropriate for large scale general purpose systems.

A different approach is given in [MLN<sup>+</sup>06] by Mutyam et al., where the authors propose to identify thermal hot spots using software, as it is the software that determines the order and the frequency of accesses to different hardware components. The focus of the work is to provide compiler-based approach to make the thermal profile more balanced in the integer functional unit through load balancing. This can be in direct conflict with the idea of using the idleness of components to put them in a low power state, so appropriate load granularity should be found in order to reach the balance between the two. It is important to point out that this process is made without any performance loss, while the peak temperature is lowered by up to  $14^{\circ}C$ .

<sup>&</sup>lt;sup>1</sup>The calculations leading to these estimations are in Attachment D4.1.1

#### 3.1.3 Register-file Energy Reduction

As mentioned above, the register file is accessed frequently, thus its energy consumption can become significant. For this reason, several techniques for reducing its energy consumption have been presented. However, they mostly rely on a specific hardware feature, which means that their applicability is limited.

One of the first ideas was to put in hibernation the registers that are not being used, given that applications typically use only a small part of register file [AVLV03]. This of course has to be supported by the hardware that should provide the possibility of turning off separate components. Similar work by the same authors seeks to reduce the number of read and write ports in a register file, reducing energy without significantly impacting performance [ALV05]. This is achieved through a combination of changes to the micro-architecture, and in the compiler, modifications to the register assignment strategy and the use of loop unrolling.

Another work [JOA<sup>+</sup>09] proposes optimal register caching in the architectures that support it. Register caching usually implies the necessity of adding extra logic to keep track of the information necessary for optimal caching, e.g., recent past or in-flight instructions, which means increased energy budget and higher chip price. Instead of adding extra logic, in this work it is proposed to keep available the information about complex data dependencies generated by the compiler, so it can be used for optimal register caching at run time. This information is added to unused bits in ISA. In this way, they achieve reduction of energy by 13%, at the same time increasing performance by 11%.

A subsequent work [GKD11] goes even further in proposing a register hierarchy. Different allocation algorithms are presented, all based on sharing temporary register files between concurrently running threads. In this way they were able to reduce register file energy by 54%. Having in mind that in GPUs register file can consume 15-20% of dynamic energy, in this way they are able to achieve up to around 10% decrease of dynamic energy.

Another work tries to take advantage of so-called transport triggered architectures (TTA) [SHMC12], where the program has control over the datapath. In this way, it can reuse data stored in pipeline registers and in this way reduce the number of accesses to the register file. In this work the authors go even further by adding a backend to the compiler that performs operation-based instruction scheduling. The algorithm consists in finding the shortest path in a resource graph, where the weights of the edges correspond to the energy cost. In this way, they are able to reduce up to 80% of register file energy. However, the number of TTA-based processors is not big, which makes this approach very limited.

#### 3.1.4 Energy Efficient Compiler-based Task and/or Data Parallelization

Nowadays having multiprocessors or multiple cores on the same chip is practically the standard, which provides the possibility of both task and data parallelization. Along with the possibility of voltage and frequency scaling, as well as turning off unused components, it can bring significant energy savings. Apart from multicore systems, parallelism is also supported in Very Long Instruction Word (VLIW) architectures through Instruction Level Parallelism (ILP), or in Digital Signal Processors (DSP) through ILP or Single Instruction Multiple Data (SIMD) instruction format. In the following we will present the role a compiler can take in this process.

One of the first works on this subject is presented by Azeemi [Aze06]. The author starts from the idea that performance and energy issues in embedded systems arise from inappropriate way software uses hardware. The work is tested on VLIW architectures, where up to five instructions can be executed at the same time. Thus, this work is an illustration of taking advantage of ILP. The compilation is implemented as iterative compilation, where the idea is to implement various versions of the same code using different optimization techniques, and select the best one. This process is implemented as multiobjective genetic algorithm, where the objectives are performance and energy, which are modeled using different monitors, such as code size, execution time, cache misses, etc. In order to maintaing the compilation time within reasonable bounds, search space is pruned using a heuristic. With this approach, they were able to achieve performance improvement of up to 80% for different benchmarks, with energy savings of up to 45%. However, all optimizations techniques are performance based, and it seems that the energy in this work is an additional benefit, rather than an objective.

In a similar way, the work of Lorenz et al. [LMD+04] represents a first attempt to generate SIMD instructions using a compiler through a vectorization step. This has allowed them to achieve on average 72% of energy reduction with average 76% performance improvement on a set of benchmark applications. Although nowadays it is a common thing for a DSP compiler to generate SIMD applications, this work is a good illustration of the benefits it provides for both performance and energy.

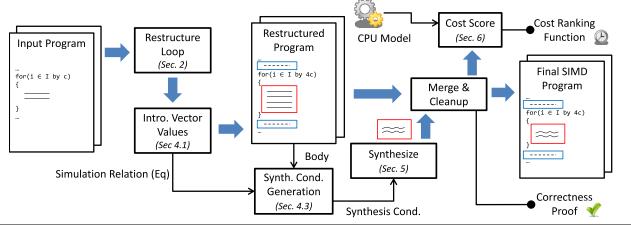

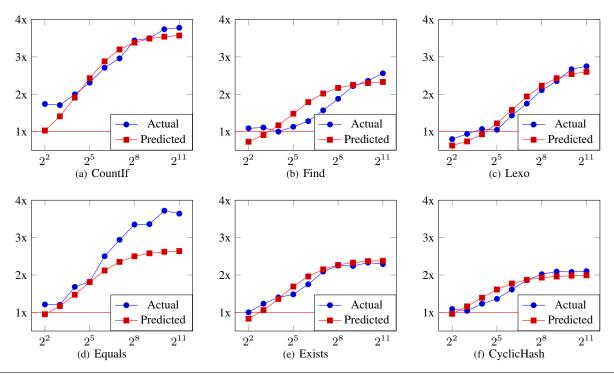

However, existing pattern-based compiler technology is unable to effectively exploit the full potential of SIMD architectures. In order to overcome this limitation, a new program synthesis based technique for auto-vectorizing performance critical innermost loops is presented in [BCG<sup>+</sup>13]<sup>2</sup>. The synthesis technique is applicable to a wide range of loops, consistently produces performant SIMD code, and generates correctness proofs for the output code. The synthesis technique, which leverages existing work on relational verification methods, is a novel combination of deductive loop restructuring, synthesis condition generation and a new inductive

<sup>&</sup>lt;sup>2</sup>Appears as a Attachment D4.1.2

synthesis algorithm for producing loop-free code fragments. The inductive synthesis algorithm wraps an optimized depth-first exploration of code sequences inside a CEGIS loop. The technique is able to quickly produce SIMD implementations (up to 9 instructions in 0.12 seconds) for a wide range of fundamental looping structures. The resulting SIMD implementations outperform the original loops by 2.0-3.7. Although the technique is mainly applied to execution time optimization, it can also reduce energy consumption.

The connection between task parallelization, voltage and frequency scaling and selective turning off of different components on a multicore chip is investigated in the work of Cho and Melhem [CM10], which derives fundamental formulas to describe the connection between parallelizing an application, its performance and energy consumption.

A concrete implementation of this approach is given by Chen et al. in [CDYW05]. The main idea of this approach is to use load imbalance of parallel applications, i.e., the fact they will not finish their part at the same time and some of them will have to wait for others to finish, and modify voltage and frequency of separate processors such that they all finish their task in (approximately) same time. Apart from parallelizing a serial application, the compiler has two more tasks: it should perform load imbalance analysis, i.e., estimate the load of each parallel and serial fragment, and in the second step calculate the voltage and the frequency of each core, so they all finish their task at the same time. However, since in many cases the load depends on input data, it cannot be estimated at compile time (in the best case its function on the input data can be inferred), which makes this approach inapplicable in these situations.

A continuation of the same idea is presented in [OKC11] by Ozturk et al. The idea of this work is to provide compiler support to multimedia embedded applications (characterized by a great number of nested loops) on the chips with voltage islands, i.e., different areas of the chip with their own variable power supply. Their work is also based on load imbalance. However, they go further by identifying the main source for this in multimedia applications to be loop bound based imbalance. This is the only type of load imbalance that could be estimated at compile time.

This work further exploits both data parallelism, i.e., performing a similar computation on different data, by executing a given loop nest in parallel on different cores, and task parallelism, by dividing a given loop nest into independent parts (if possible), and executing each of them on a different core. After mapping each nested loop and its parts on different cores, the second step is to estimate the load of each core. In order to do this, the compiler should perform two calculations:

- 1. Iteration count estimation

- 2. Per-iteration cost estimation

The first step is not very difficult, given that in most array-based applications loop bounds are known before the execution starts, or they can be estimated through profiling. The second step is more complicated, and in general case can be estimated using a Worst Case Execution Time (WCET) technique, which is well known. The approach used in this work is based on the number and the type of the assembly instructions used in each loop.

After having estimated load of each core, the voltage of each one is assigned in the following way. The one with the biggest load will have highest possible voltage, the second one will have the lowest possible voltage that does not increase the total execution time, etc. In this way, they were able to reduce energy consumption by 40.7% on average, achieving at the same time 14.6% average performance improvement in the terms of the total number of execution cycles.

#### 3.1.5 Code Motion for Energy Optimization

Code motion means rescheduling or reordering execution of instructions, while preserving the functionality of the code. In many cases energy saving can be achieved by code motion. In the real world, programmers are seldom aware of the hardware energy-usage implications of a particular ordering at runtime, and this often leads to loss of energy-saving opportunities.

There are two basic scenarios in which code motion can play a key role in reducing energy consumption: in optimising time-critical code and in smoothing workload spikes. A section of code may be time-critical due to its role in inter-process communication, a real-time I/O response or other time-critical operation. If code in the critical session, which is irrelevant to the critical operation, into the non-time-critical session, can facilitate run-time energy optimization, as shown in the following example, relating to "user-perceived time" [SSCK14].

To explain user-perceived time, we take a look at one interactive session (e.g. a click on a button or slide on the screen). The user first feeds in an input, and the system will render a UI response after a period of processing. The interval between user input and UI response is the so-called "user-perceived time". In most cases, there is some "think time" between the UI response and the next user input. As far as the user is concerned the UI response should be as fast as possible (it is "time-critical") whereas the user is most likely oblivious to the processing during think time. Thus we can apply aggressive runtime optimization (e.g. slowing down processor frequency) during the think time. Further, we can delay code that is irrelevant to UI response (code motion) so that processor frequency can be reduced during both think time and user-perceived time, while still guaranteeing timely UI response.

The second basic scenario mentioned above concerns workload spikes. A heavy workload that comes in a short time slot causes workload spikes. Due to sluggish (coarse-grained) runtime power adaptation, the processor needs a high frequency level to deal with workload spikes;

however, keeping the same high level even between and after the spikes leads to a waste of energy. To reduce workload spikes, high power instructions should be spread over a long period. There are many challenges and trade-offs to be addressed, such as preserving the user experience.

Performing code motion is in general a complex task. In the simplest case (in one single code block), code motion consists of delaying instructions that are irrelevant to the critical statement(s) (i.e. the statement responsible for time-critical operation) until after the critical statement, but respecting dependencies of other statements on the delayed instructions. That is, an instruction cannot be delayed until after another instruction that depends on it. It is tricky to find the relevant code for the critical statement, which is the same process as find the irrelevant code, and the process is formally called program slicing [Wei81]. A program slice consists of the parts of a program that (potentially) affect the values computed at some point of interest. The calculation of the slice is based on the Program Dependence Graph (PDG) [HRB88], which consists of the Control Dependence Graph (CDG) and the Data Dependence Graph (DDG). A statement is in the program slice for the interested statement if there is a path connecting them in the PDG.

In inter-block cases, there are many trade-offs. For example, moving code out of a loop may induce more spikes due to frequent processing of high power instructions without interspersing low power instructions around them in the loop. Accurate energy modelling is needed to evaluate the benefits of code motion in more complex cases.

#### 3.1.6 Superoptimization

Traditional compilers optimize code during compilation, however, they only produce improvements over the existing code instead of truly optimal code. Superoptimization is a technique developed by Massalin [Mas87], allowing an optimal section of code (for a given metric) to be found for a given function. By searching through all possible instruction sequences and checking whether the target instruction sequence is equivalent, an optimal piece of code can be found.

Massalin found that by applying superoptimization sequences of code were found, which exploited the processor's features in unusual ways. These sequences of code made use of the flags, along with combinations of arithmetic and bitwise operations.

```

1

int signum(int x)

d0 = n

2

add.1 d0, d0

3

3

if(x > 0)

subx.1 d1, d1

4

4

return 1;

negx.1 d0

5

else if (x < 0)

addx.l d1, d1

return -1;

6

d1 = signum(n)

else

8

return 0;

9

}

```

The code above on the left shows one of the functions Massalin optimized, with the resulting Motorola assembly on the right. The resulting assembly makes use of the carry bit (x) to perform the computation. The carry bit is set by the first operation if the input is negative, and this bit is propagated into d1 in the next instruction, which computes d1 = d1 - d1 - x. The third instruction negates d0, which sets the x bit if d0 != 0. Finally the values in d1 and x are combined to give the result. The optimal version of this function was shorter than any previously found instruction sequence — an expert writing the same sequence managed to reduce it to 6 instructions.

In general superoptimizers have a similar structure:

- 1. Enumerate the instruction sequence.

- 2. Test the instruction sequence.

- 3. Cost the sequence.

When the entire set of instruction sequences has been enumerated, the instructions can be ranked and the lowest one selected. Often superoptimizers will attempt to enumerate the sequence in cost order, allowing the first equivalent sequence to be selected and the search stopped. In the case of optimizing for code size this is simple — the instruction sequences are generated in size order. This method becomes more difficult if targeting performance or energy consumption.

Some superoptimizers have attempted to reduce the size of the search space by canonicalizing register namings [BA06], by restricting the number of constants used [GK92] and by removing redundant instructions (such as X = Y, Y = X) [Mas87].

Testing the instruction sequence is a challenging problem, as it must be done fast, yet ensure that the instruction sequence is equivalent for all inputs. One approach taken by many superop-

timizers [BA06, SSA13] is to test the instruction sequence on a few test vectors, and if it passes all of them, verify the sequences are equivalent using an SMT solver.

Other approaches have attempted to guarantee the instruction sequence is correct by construction — this incorporates steps 1 and 2 together. Gulwani et al. [GJTV12] use a solver and counter example guided inductive synthesis to connect multiple 'components' together to produce similar types of programs to Massalin's superoptimizer. A similar approach is taken in [BCVF06] using answer set programming to produce a set of instruction sequences.

There are currently no superoptimizers which explicitly target energy consumption, although improvements in energy consumption may be expected from reducing code size, and increasing performance.

#### 3.1.7 Other Important Techniques

Provided that the compiler has insight into energy consumption, other common compiler techniques could be used taking as objective energy rather than performance. For example, peephole optimization, which changes a piece of code with another that carries out the same task, can perform the change in a way the new code consumes less energy. In general, it is possible to have different versions of the same code, and at compile time decide which one to use. Also, if precise energy consumption cannot be estimated without the data, with the use of Just In Time (JIT) compilers it is possible to decide which is the most optimal version of the code (in terms of energy) at run time and continue its execution. However, this introduces certain time overhead at run time. In the following text we will see some examples of algorithm and/or code transformation that can provide energy savings.

In a similar way, instructions can be scheduled so as to reduce the energy, given that the state of the hardware, as a direct result of the previous instruction, also affects on its energy consumption. An example of this is so called *cold scheduling* [SyTD94], whose aim is to reduce interinstruction effects. Another example is given in [PKVI00], where Parikh et al. can save up to 17% of energy through optimal instruction scheduling.

Finally, the compiler should be aware of the hardware and the possibilities it provides. For example, if there is a floating point unit, the compiler should generate the code that uses it. Thus, the back-end should be designed, or optimized if possible, in such a way that it takes advantage of all hardware possibilities.

#### 3.1.8 Summary of Used Static Analysis Techniques

We will now list all the static analyses used by the above-mentioned compilers as inputs to the optimization step, or identified as a necessity:

- Energy accounting (energy transparency), i.e., providing insight into the amount of energy a piece of code spends, in order to enable the evaluation of different optimization techniques

- Inferring the time (starting and ending point) the components (e.g., disks) are not active, which can be used by the OS to turn them on and off in a timely manner

- Identify parts of the code the processor can be slowed down with no performance loss, e.g., memory access, as an enabler for voltage and frequency scaling

- Load imbalance analysis, as a special case of the previous item

- Execution time estimation, as another enabler for voltage and frequency scaling

- If there is more than one resource for a certain action, find the shortest path to it (in the terms of energy)

#### 3.1.9 Concluding Remarks: Compiler Optimization Techniques

In this section we have presented few representative compiler optimization techniques. The most important observation is the lack of energy accounting which would provide the compiler the necessary insight into the quality of each optimization technique without having to perform simulation and/or measurements. On the other hand, although there are lots of different examples, there is no general approach that would combine different techniques in order to obtain overall energy minimization. As we have seen, some techniques can have positive impact on the consumption of one part, but may increase the consumption of another. For this reason, it is important to treat the optimization problem on a global level. Finally, the compiler should be aware of the underlying hardware in order to be able to use all its potentials for saving energy.

## 3.2 Algorithm and Source-Code Energy-aware Optimizations

In this section we will present solutions aimed at optimizing energy through algorithm or high level code modifications. We have identified the following major trends among modifications:

- Re-computation vs. Communication

- Code level parallelization

- Trading precision, or Quality-of-Service (QoS), with energy

#### 3.2.1 Re-computation vs. Communication

Technology scaling has been more beneficial to transistors than to wires. For this reason, communication has become the limiting factor of both power and performance [MG08], especially bearing in mind its growing significance in today's multi-core era. Even the introduction of the Network-on-Chip (NoC) paradigm [BWM+09] does not solve the problem completely, given the growing trend of communication requirements.

A solution to this problem is to perform re-computation of some information, rather than fetching it from a remote place [MG08]. An important enabler for this approach is to develop greater understanding of algorithms and data structures in order to better manage data movement in systems. Furthermore, it is important to be able to estimate the cost of both computation and communication in order to be able to decide which one is more beneficial in particular cases. The authors believe that the significant work done in VLSI domain in characterizing and predicting interconnections can be helpful in understanding communications in multi-core processors.

The great majority of publications on the subject have the objective of increasing performance by trading re-computation for communication. Although without knowing their energy cost we cannot claim that these techniques provide energy savings as well, they can be a good starting point.

One example is given in [RK08], where Rolf and Kuchcinski give a solution to a parallel depth first search algorithm, where they show how reducing communication at the expense of increasing computation can achieve speed-up of up to 18 times. They also claim that less communication gives more room for an advanced load balancing scheme, which can further improve performance. As we have seen above, load balancing can also be used to reduce energy.

Another example consists in honouring multiple alignments, i.e., relative allocation within an array, when decomposing data into distributed memory [GSB95], which reduces conflicting alignments and in this way the communication. The performance increase is 80%, which becomes more significant bearing in mind that when it was published (1995) communication did not represent such a significant overhead.

#### 3.2.2 Code Level Parallelization

As previously mentioned, executing code concurrently on multiple cores can be energy efficient [KA10, KA11, KA09a]. It is also possible to optimize performance through static energy-bounded scalability analysis [KA09b], given an energy budget. Similarly, devices capable of parallelism through hardware multi-threading may require some level of parallelism in order for a core's energy efficiency to be maximised [KE13, SB13].

Although the process of parallelization is often performed automatically by the compiler, parallel code can be developed manually by the programmer. This process can be time-consuming, complex, iterative and error prone, yet it is more flexible and it can be the only solution if the compiler is not capable of generating parallel code. An extensive survey of parallel programming models and tools can be found in [DMCN12].

#### 3.2.3 Precision (QoS) - Energy Trade-off

In the recent past some researchers have studied energy-accuracy trade-offs [LY07]. The main conclusion is that there are applications in which a significant proportion of energy is spent on providing a *correct* result, whereas the applications are resilient to error [LY07, MSHR10]. One of the most important conclusion from these studies is that there are parts of applications that are resilient to errors, or provide a result that is good enough, while there are parts that need to have the precise result.

This idea is exploited in the design of EnerJ [SDF+11], an extension to Java which provides a solution for isolating precise parts of the program from the ones that can be approximated by introducing approximate types, i.e., type qualifiers that declare that the data can be used in approximate computations. The system can use this information as a sign to use low power storage, low power computation, or even low power algorithms provided by the programmer. Furthermore, the system can statically guarantee the isolation of precise program parts from the approximated ones, which eliminates the need for dynamic checking and the additional energy consumption implied with it. In this way, energy savings of 10% to 50% can be achieved.

However, in order to provide the practicality of the approach, it has to be supported by the hardware as well. The authors propose an ISA extension, where the additional bits would show if the components that support the execution of the approximate code should be involved in the current calculation. They also envision the existence of separate ALU and floating point units for both approximate and precise operations. Furthermore, the cache lines should have an additional bit for distinguishing the approximate from the precise ones. It is also proposed to supply the approximate memory (SRAM) with lower voltage, or refresh DRAM with lower frequency, etc. However, the additional hardware would lead to extra chip fabrication costs. Thus, in order to support the practical exploitation of EnerJ-like proposals, it should be evaluated when is the additional hardware cost justifiable.

An important contribution to this line of research has been provided by the Computer Science and Artificial Intelligence Laboratory from MIT [MRR11a, MRR11b, ZMKR12, MSHR10, RHMS10]. Their work started with the idea of supporting the execution of a task in the case of having to cope with limited resources, failures, etc. [RHMS10], and eventually it evolved to the

idea of providing optimal accuracy-resource consumption trade-offs [ZMKR12], where resource can be time, energy or cost. It is clear that in the case of energy an important enabler for this process is the estimate of energy consumption. Another important enabler is the awareness of which parts of the algorithm permit lower accuracy, i.e., in image processing pixel values can be approximated, but the part of the code that determines how to reconstruct the image has to be accurate.

The examples of accuracy-aware transformations they give are task skipping (in parallel applications) [Rin06], loop perforation, i.e., executing only a subset of the original loop iterations [MRR11b, Aga09, SDMHR11], approximate function memoization [CGL10], substitution of multiple alternate transformations [BC10], such as shifting left or right instead of performing division or multiplication, or sampling, which assumes discarding certain computations. In the case of reduced resource computing, we could also add cyclic memory allocation [NR07], where a fixed sized buffer is allocated for a given dynamic allocation site. These transformations provide the possibility to realize different optimization problems, such as to minimize resource consumption subject to a given accuracy, or to maximize accuracy subject to a given resource consumption. A solution to these optimization problems is given in [ZMKR12], while in [MRR11b, MRR11a] a probabilistic reasoning that justifies that the application of transformations may change the result within probabilistic accuracy bounds is given for the case of loop perforation.

The same research group also provides PowerDial [HSC<sup>+</sup>11], a system that dynamically adapts the application to the varying characteristics of the environment (in terms of load, power, resources, etc.). In essence, it is based on a set of static configuration parameters which can be transformed into *dynamic knobs*. The dynamic knobs can be further tuned by the control system to change the configuration of the running application in order to trade off accuracy of the computation in return for the computation resources the application needs. Although automatic, this technique requires the user to provide training data, an output abstraction and identify a set of parameters (static configuration parameters) and their range in the program.

#### 3.2.4 Summary of Used Static Analysis Techniques

The enabler for all the deployed techniques is again the estimation of the consumed energy. Other static analysis techniques use to enable the code transformation are the following:

- Understanding communication patterns in order to enable communication re-computation trade-off

- Static energy-bounded scalability analysis, which optimizes performance of parallel algo-

rithms given an energy bound

- Static verification of approximate and precise code computation, in order to enable EnerJlike applications

- Probabilistic reasoning which justifies that the applications of code transformations change the result within given accuracy bounds, in order to enable approximate computations

#### 3.2.5 Concluding Remarks: Source Code Energy Optimization

This section has provided some insight into code transformation techniques that can reduce energy consumption. Particularly interesting is the application of approximate computation which can be applied in many applications within acceptable losses. Although it has been mostly applied to performance optimizations, it could also be applied for energy optimizations, assuming that estimation of energy consumption is available.

## 4 Optimization in the Case Studies

#### 4.1 Architecture and considerations

Before discussing the optimizations that are relevant to various case studies, we discuss architecture and system characteristics that may be exploitable for energy optimization, or conversely, that may constrain or preclude certain techniques. The classifications of optimizations described in Section 3 are referenced where appropriate.

Exploitation of available parallelism can be achievable at various levels, but the best to apply may be architecture and program specific. For example, VLIW DSP processors benefit from aggressive instruction scheduling. The instruction set and processor pipeline are designed to exploit instruction level parallelism, and the signal processing they perform fits well to this structure.

In the case of the nominal target for these case studies — the XS1-L — there is a reasonable amount of parallelism possible per core (up to eight threads), but no instruction level parallelism. However, there are combined arithmetic operations such as *multiply-accumulate*, which speed up common data processing operations. Further, for Input/Output, port resources can handle some data manipulation tasks, such as buffering, timing and serialization.

#### 4.1.1 Thread parallelism

In [KE13] the energy efficiency of the XS1-L in relation to the number of utilised threads is discussed. If fewer than four threads are utilised per core, then the pipeline is under-used, resulting

in sub-optimal energy efficiency. As such, this motivates keeping the pipeline full whenever the processor is active, by having four or more active threads. This is true of other architectures with parallel features, such as the Xeon Phi [SB13], which has sub-optimal efficiency if fewer than two threads are running on a core.

The methods by which maximum pipeline efficiency can be obtained is governed by the dependencies and structure of the application. As such, for each case study, optimization strategies may differ.

In terms of the overhead of parallelizing in the XS1-L, at least three instructions are required to create a thread, and further instructions may be required in order to setup all registers such as stack, data and constant pointer. This constrains parallelization optimizations that would create new threads, to ensure that the work they will perform is sufficiently large compared to the thread creation time. Alternatively, provided there are sufficient thread resources available, the threads may be permanently allocated, and wait for work to be communicated to them.

Beyond maximising pipeline utilization, another possible outcome of optimizing for thread parallelism is that it may then be possible to lower the processor clock frequency and voltage. The application remains able to deliver the required performance (e.g. the same data throughput), whilst consuming less energy, a trade-off discussed in Section 3.1.1.

#### 4.1.2 I/O and computations

Some architectures have been designed so that real-time I/O and communication can be scheduled relative to computation. One of our target architectures (the XS1-L processor) is a good example of this. The central idea is that when programming the system, the program is seen as a sequence of I/O operations and computation operations:

```

Perform some computation

Perform some I/O

Perform some computation

Perform some I/O

```

When an architecture is designed to dissociate I/O and computation, then the precise timing of the I/O is no longer an issue: the I/O instruction has to be reached *before* the required time; but not *at* the required time. This means that the computation has to be *fast enough* to perform the I/O on time, but it can be made to run faster without affecting the semantics of the system.

Architecturally, I/O and computation can be dissociated by triggering the I/O on a particular clock cycle (for example, the next clock, or the fifth clock), or by not allowing the I/O to proceed until some external event has completed, (for example the first clock where a handshake wire has

been asserted). Note that in many architectures this is not the case, and I/O has to be delayed to the appropriate time by inserting no-operation instructions (NOP) in the instruction stream.

Dissociation of I/O and computation is important from a power perspective as it enables both the programmer and the tools to schedule computation tasks around the I/O instructions; and the only constraint is that the I/O instructions are reached in time, and that any data dependencies are maintained. If these goals are met, then given a fixed throughput of the processor, it can be proven that the system will work. Conversely, given knowledge as to how much slack there is in the system, the clock frequency of the processor can be delayed so that the computation finished *just in time*; which in turn will enable us to lower the voltage, and make significant power savings. Having sequences of no-operations inserted take this freedom away, or put the responsibility completely in the lap of the software engineer.

A further optimization is to exploit parallelism between I/O and computation. If I/O and computations have been dissociated, then as a buffer between the two will enable computation to continue, whilst the I/O unit is ready to perform the I/O; synchronising on the next interaction, at which case the computation has to wait for the previous I/O operation to complete. This gives further opportunities for scheduling computations.

#### 4.1.3 Core parallelism

Where multiple cores are used, voltages and frequencies can be optimised per core. Various of the techniques discussed in the previous section may be used or combined for optimising, where there is core-local parallelism, multi-core parallelism, and inter-core communication to consider. In particular, consideration should be given to re-computation vs. communication (Section 3.2.1, as well as task parallelization (Section 3.1.4).

## 4.2 Economics of power optimizations

As stated before, energy use can be optimised by using a multitude of cores that run slowly. Given the limits of voltage scaling, the physics of leakage, and the extra costs incurred in communication, an optimal number of cores can be estimated that will solve a problem using the least energy. However, from a commercial perspective this is not always desirable as deploying extra hardware costs money.

Indeed, when designing a system, the designer is often given budgets within which to stay. In the case of a mobile system, the budget will be for the for the maximum weight and size, the maximum bill-of-material cost (the BOM cost), and the minimum time that the system can operate on a single charge. In the case of a non-mobile system, the budget may be the energy

usage and bill-of-material costings (the BOM cost). In that case, the energy usage is often guided by legal requirements. This may be the required maximum stand-by power usage, or a desired efficiency label.

In either case, power does not need to be optimised beyond the point where it is "good enough". Reversely, it may be that parallel tasks have to be combined in order to reduce the system cost; the designer may have gone over the cost-budget, but be below the power-budget. All optimizations have to be balanced too; when all budgets are met, it may make sense to make system half the cost whilst decreasing power efficiency by 5%; or it may be worthwhile to increase cost by 5% in order to double power efficiency.

## 4.3 Real-time audio processing

A good case to address with the aforementioned techniques is the design of a mobile audio device; such as a battery powered headphone amplifier. Although traditionally an analogue product, headphone amplifiers are now systems that contain both analogue and digital components. The analogue components are an analogue amplifier, an amplifying Digital to Analogue Converter (DAC) that generates the analogue signal for the headphone, a Phase-Locked Loop (PLL) that generates a precise clock for the DAC, and a USB-PHY to receive digital data. The digital component is typically a processor that executes the following tasks:

- A USB component that communicates with a mobile phone or tablet to receive audio data. Software on the phone will decide as to what audio is played.

- A DSP component that will perform some operations on the data; this may, for example, be sample rate conversion, converting sample formats, or performing sound enhancement.

- An audio delivery component, that typically drives digital data to the DAC and a base-line clock to the PLL.

Although a sizeable fraction of the power gets used by the USB PHY and the analogue amplifier, designing the software to be low power has a measurable effect on the life time of the battery. This optimization is at present very much a manual effort.

The three software components have different characteristics in terms of their energy requirements:

• The USB component is heavily optimised, and only little room is available for energy optimization; mostly in the form of deploying an extra core and thereby allowing the USB core to be slowed down and scale its voltage.

- The Digital Signal Processing component can be subjected to a variety of optimizations, in particular parallelization and precision trade-offs.

- The sound delivery component is likely to benefit from I/O parallelism and scheduling; although the current component has been hand crafted, clearer components could be written that could be subject to scheduling.

Manual optimization of the system as a whole shows an interesting set of challenges:

- Voltage and frequency scaling applies to the system as a whole; as such, the system that

requires the highest frequency sets a limit for the system as a whole. In this particular case

study, the system is likely to be limited by the frequency required by the USB software.

- The Digital Signal Processing component and the I/O component are likely to be opposite ends in how power saving is to be applied. From experience, it is best for the DSP to be parallelised (and reduce its frequency at the cost of a few extra threads), whereas the I/O could be combined into a single thread, because each of the tasks is very little work. Not combining them would be expensive and not save power.

- The system as a whole comprises components that work on different sorts of data. The analogue delivery component works with 24 bit data values stored in the upper 24 bits; the DSP component way work on similar values or may work on high frequency 1-bit DAC values that use all 32 bits in a word, and the USB component may be processing packed data (all 32 bits are used), unpacked data (with the data in the top 24 bits), or 1-bit DAC data (all 32-bits used). There may be value in scheduling those tasks or locating those tasks on appropriate threads and cores.

Hence, this case is interesting because it will enable optimization strategies to be explored individually, but there is also insight to be gained from a whole systems perspective.

This system should be optimised primarily for dynamic current consumption. Static current is not relevant since the owner of the system will switch it off when they are not listening to music.

#### 4.4 Robot and motor control

In this area, we focus on driving small motors, where computation is a significant component of system power consumption; in particular we consider:

• a multi-axis system that requires the logic to control the positioning of a multitude of (small) motors;

- motors where the peak power consumption is in the order of no more than a few Watts each;

- motors where the standby consumption is likely to be less than a Watt each.

This makes it worthwhile to reduce the power consumption of the digital part; in particular if the system as a whole spends sufficient time idling. The system typically comprises a motor, a transistor bridge to drive each end of the motor, an ADC to measure current on each end, and a processor that executes the following tasks:

- A PWM driver that generates a Pulse Width Modulated signal for each end of the motor. A PWM signal is a digital approximation of the analogue signal, and it is used to drive the transistors in the bridge. The PWM signal may either be generated by a special hardware component (as found on system-on-chip motor control devices), or by a software component (such as found on software controlled devices). The latter consumes more resources, but gives finer-grained control to the programmer.

- A Digital Signal Processing component that given

- the currents as measured by the Analogue to Digital converters, and

- the desired torque

control the PWM values as applied to the motor. This can be as simple as a series of matrix transformations.

- A controller component that controls the speed and position of each of the motors; this can be as simple as a Proportional Integral Differential controller (PID) which comprises only a multiplications and additions.

- A multi-axis controller that computes the desired positions and speeds of each motor, in order to create a single smooth motion.

These components may be distributed over the system in order to build a modular and extensible system. In that case there will be one digital processor for each motor in a multi-axis system that executes the first three of the software components. A single central processor will implement the final component.

In terms of optimizations, different techniques will apply to different parts of the system. If the system is designed in a distributed manner, then voltage and frequency scaling can be applied individually to the various distributed components of the system. At present, no effort has been spent on optimising the software stack, as it has only been applied to high powered motors. Optimizations are expected to be valuable across the software components, as there is an imbalance in computation and IO requirements:

- If the PWM driver is implemented in software, then it has very little work except for making sure that signals are switched at precise times. As such, there is scope to schedule this by parallelising the IO with a different task.

- The Digital Signal Processing component performs a reasonable amount of computation, and does so in lock step with the PWM driver and ADC samples. As such, it may be able to shift work from this task into the PWM task (or combine them and then parallelise them) in order to create a balanced workload that can run at a reduced frequency.

- The controller represents a very small workload. This poses an interesting problem that

occasionally extra work needs to be performed, and the system needs to be sized to allow

for that extra work.

- The multi-axis controller is a significant workload that can be optimised by splitting it out and potentially over multiple cores. It has a soft real-time requirement as it executes only to plan activity. This plan is then executed by the other software components. The multi-axis controller traditionally relies on floating point computations that may be optimised into fixed point computations for processors that do not have hardware floating point units.

In addition to the above optimizations, there is an interesting precision trade-off; driving motors with higher precision will reduce their power consumption. So a trade-off is made between the amount of computation performed digitally, and the power consumed in the analogue part. This is likely to be outside the scope of the project.

This system is likely to be running permanently; as such the important metric for optimization is the dynamic current. Peak power is interesting, but is likely to be close to the average power consumption.

## 4.5 Real-time networking

The purpose of real-time networking is to deliver data at a guaranteed time. The purpose of real time networking ranges from control in industrial production lines, through to the reversing camera of a car and or the sound distribution in a music arena. In some cases very low power nodes are required, for example when designing a sensor network for example.

The real-time network that the project can look at is ones that are based on the IEEE 1722 standard for "Layer 2 Transport Protocol for Time Sensitive Applications in a Bridged Local

Area Network". This protocol was developed as a protocol for Audio and Video delivery, but is also useful for other data, for example sensor and control data in an industrial context.

A real-time networking system typically comprises a networking PHY (we will just assume some sort of Ethernet PHY; probably one of the low-power 100 Mbit PHYs), a digital processor that implements the standard, and one or more IO devices that are controlled or observed through the real-time network. The latter are application dependent, and may be amplifier units for the music arena, or a motor control system in an industrial setting.

The digital processor executes the following tasks:

- Data transmission and reception tasks; these may be bespoke hardware in SOCs, or maybe software on general purpose processors.

- A receive filter

- A MAC layer for reception

- A traffic shaper/MAC layer for transmission

- An implementation of the Stream Reservation Protocol and Media Reservation Protocol (SRP and MRP).

- An implementation of the control protocol defined in IEEE 1722.1

- An implementation of a peer-to-peer clock protocol.

- An implementation of the AVB protocol in the form of a listener and/or a talker.

- A program that communicates with the target logic.

As far as the software is concerned, many components can run as slow as is sensible; the only real time requirements are that the tasks that operate on data (that is the MAC, transmission, reception, and IO layer) have sufficient bandwidth to deal with the average data rate, and the transmission and reception layers have sufficient bandwidth to deal with the peak data rate.

This means that there is scope to run many tasks at a very low frequency, and only a few tasks at high speed. In particular:

• Data transmission and reception tasks; if these are implemented in software, then they must be designed to be able to keep up with the line rate of the physical network medium (100 Mbit, or 10 Mbit for slow systems).

- The receive filter just has to keep up with the line-packet-rate; that is, it must be analysed

for being able to parse headers and test headers at line rate (for minimum sized packets

that is approximately 150 kPackets per second for a 100 Mbit line rate).

- The MAC layers have to be able to keep up with the average data rate expected on the node; typically well below line rate.

- The SRP, MRP, and 1722.1 control protocols run with time-outs of tens or hundreds of milliseconds, and must be analysed to complete in time for that. They can also run to completion if that is more efficient.

- The peer-to-peer clock protocol expects precise timestamps from the data transmission and reception tasks, but can itself run at a low frequency, needing to complete only in 10s of milliseconds.

- The implementation of the talker and listener have to be able to deal with the average data rate of the payload, excluding headers.

A completed analysis of all tasks will yield minimum speeds that will all be quite low, except for the direct transmit and receive tasks. These tasks may be combined and executed in a single task, or offloaded to a secondary very slow core.

There is little scope to manage precision or hamming distances.

None of these optimizations or analysis have been performed manually; at present the software stack runs at full speed.

This system should be optimised primarily for dynamic current consumption and static current consumption; the peak power demand should be estimated but need not be optimised. The system is likely to have phases of activity, which means that energy use will be a combined version of static and dynamic power figures. Peak performance is important, as we expect fluctuation of power demands when packets arrive or are transmitted (which may happen simultaneously).

## 5 Assessment and Relation to Future Tasks

In this report we have surveyed many energy-related optimizations that can be obtained by static software improvements. That is we have surveyed ways in which code can be transformed during development or at compile-time to reduce various aspects of energy usage. Different energy metrics were discussed in Deliverable D6.1 of the ENTRA project [Mul13]. As expected, most optimizations are dependent on features of the underlying architecture, instruction-set and the availability of hardware power-saving features. In Section 3 the survey considered optimizations

for a wide variety of platforms, while in the Section 4 we focus on general features of, and optimizations for, the ENTRA project target platform, namely the xCORE family of processors produced by XMOS Ltd.

## **5.1** Focus areas for future research on optimization (WP4)

While there is a significant overlap between performance optimizations and energy optimizations, there are opportunities for energy optimization where execution time may be unaffected or even degraded. Static execution time optimization has been studied intensively for a long time, whereas energy optimizations that are independent of performance are generally speaking less understood and researched. Such optimizations are especially significant for the ENTRA project.

The opportunities for optimization in the case studies suggest the following focus areas for research in the coming months in WP3 (Analysis) and WP4 (Optimization) of the ENTRA project. Most of the gains are going to be made by choosing an appropriate level of parallelism in the system. In the following paragraphs we summarise the directions and ongoing research tasks.

Scheduling of communication versus computation. A rule of thumb for energy optimization, which is being applied to the case studies, is to ask "how slow can a computation run in order to meet the application's internal and external communication requirements?". To answer this question requires subsidiary analyses to those considering energy directly. The analysis should expose essential dependencies of the communicative structure of an application, and the (probabilistic) rates of communication and computation. The aim is to allow communication and computation to be scheduled optimally, without unnecessary delays and ensuring that time-critical communications are made "just in time". Related optimization principles relate to task location; tasks that communicate frequently should be located as physically close to each other as possible, and threads with similar timing requirements should be on the same core.

Trading off parallelism against other costs. Introducing as much parallelism as possible, and running processors slower as a result, is a principle that can lead to significant energy savings. However, parallelism usually comes with overheads of communication, replication of data, and synchronization delays, as well as expense in manufacture and materials. Thus, analyses of the case studies that allow these trade-offs to be evaluated are important for optimizations based on parallelism. Other aspects of parallelism to be investigated, looking beyond optimization for the xCORE, includes fitting code to what the hardware offers, such as the number of threads in software and hardware. In this work we aim to look also at GPUs as a target as well as the Intel Xeon Phi.

**Load balancing.** Achieving the above goals for a given application requires detailed understanding of the overall thread behaviour of an application: the distribution over time of the running threads, how active or inactive each thread is, how much work each thread does for each communication with other threads and whether there are workload spikes causing high peak power consumption. Once this is understood the thread structure can be optimized to eliminate bottlenecks and synchronization delays.

**Precision management.** This is going to be of less immediate value in the chosen case studies, but it is still a valuable tool when managing energy consumption. In certain applications, energy is wasted by computing results that are more precise than required, for example using higher-precision numbers than are needed. Analysing and identifying such cases can lead to energy optimizations by reducing precision. In some cases this is a trade-off against quality; determining what quality is "good enough" is the key to making optimizations.

**Various low-level energy improvements.** We will also explore low-level optimizations applicable to xCORE and other targets, such as alignment of loops to line boundaries in memory.

## 5.2 Relation to Dynamic Optimization

As emphasised earlier, this deliverable covers static optimizations, applicable during application development and compilation. The deliverable provides input to Tasks T4.2 and T4.3 of the ENTRA project, which consider a wider range of optimizations, including dynamic optimizations. These could be for example dynamically trading off energy against quality of service (T4.2) by modifying precision or processor speed, or energy-aware scheduling (T4.3). We note here that static optimization and code design can enable more effective dynamic optimizations, for example building into the code parameters that control quality; such parameters can be dynamically adjusted to suit the perceived quality needs. We also note that energy modelling (Work Package WP2) is critical to both static and dynamic optimization.

## 5.3 Relation to Energy-Aware Software Engineering

Although this deliverable does not cover tool support, it provides input to Work Package WP1 (Energy-Aware Software Engineering) and in particular Task T1.1 (Energy-Aware Tools). Initially, tools will focus on energy transparency rather than automatic optimization. Energy transparency tools will help the developer to obtain information about the energy consumption of the program, thus assisting the developer in identifying opportunities for manual optimization.

They will also support the evaluation of optimizations. Other tools, needed to support the optimizations discussed in Section 4, are those providing information about dependencies within the program especially those relating to communication, timing, and the distribution of parallel tasks.

## References

- [AAB09] José L. Ayala, David Atienza, and Philip Brisk. Thermal-aware data flow analysis. In *Proceedings of the 46th Annual Design Automation Conference*, DAC '09, pages 613–614, New York, NY, USA, 2009. ACM.

- [Aga09] Anant; R. Agarwal. Using Code Perforation to Improve Performance, Reduce Energy Consumption, and Respond to Failures. Technical report, MIT, September 2009.

- [ALV05] José Luis Ayala and Marisa López-Vallejo. Compiler-driven power optimizations in the register file of processor-based systems. In Luca Benini, Ulrich Kremer, Christian W. Probst, and Peter Schelkens, editors, *Power-aware Computing Systems*, volume 05141 of *Dagstuhl Seminar Proceedings*. Internationales Begegnungs- und Forschungszentrum für Informatik (IBFI), Schloss Dagstuhl, Germany, 2005.

- [AVLV03] José L. Ayala, Alexander Veidenbaum, and Marisa López-Vallejo. Power-Aware Compilation for Register File Energy Reduction. *International Journal of Parallel Programming*, 31(6):451–467, December 2003.

- [Aze06] Naeem Zafar Azeemi. Exploiting parallelism for energy efficient source code high performance computing. In *Industrial Technology, 2006. ICIT 2006. IEEE International Conference on*, pages 2741–2746, 2006.

- [BA06] Sorav Bansal and Alex Aiken. Automatic generation of peephole superoptimizers. *ACM SIGOPS Operating Systems Review*, 40(5):394, October 2006.

- [BC10] Woongki Baek and Trishul M. Chilimbi. Green: a framework for supporting energy-conscious programming using controlled approximation. *SIGPLAN Not.*, 45(6):198–209, June 2010.

- [BCG+13] Gilles Barthe, Juan Manuel Crespo, Sumit Gulwani, César Kunz, and Mark Marron. From Relational Verification to SIMD Loop Synthesis. In Alex Nicolau, Xiaowei Shen, Saman P. Amarasinghe, and Richard Vuduc, editors, ACM SIG-PLAN Symposium on Principles and Practice of Parallel Programming, PPoPP '13, pages 123–134. ACM, 2013.

- [BCVF06] Martin Brain, Tom Crick, Marina De Vos, and John Fitch. Toast: Applying answer set programming to superoptimisation. In *Int. Conf. Logic Programming*, pages 270–284, 2006.