## **ENTRA**

318337

**Whole-Systems ENergy TRAnsparency**

# **Energy-Aware Software Development Methods and Tools**

Deliverable number: D1.2

Work package: Energy-Aware Software Engineering (WP1)

Delivery date: 31 December 2015 (39 months)

Actual date: 1 March 2016

Nature: Prototype

Dissemination level: PU

Lead beneficiary: IMDEA Software Institute

Partners contributed: Roskilde University, University of Bristol, IMDEA Software Insti-

tute, XMOS Limited

Project funded by the European Union under the Seventh Framework Programme, FP7-ICT-2011-8 FET Proactive call.

#### **Short description:**

This deliverable reviews the field of energy-aware software development and describes how the areas most closely related to the ENTRA project have advanced during the execution of the project. This establishes the context for a description of different activities and scenarios for energy-aware software development. Then, it demonstrates (by using a tools front end developed in the project) how the final energy-aware prototype tools for analysis, verification and optimisation can be integrated into tool-chains for energy-aware software development processes and life-cycle. Finally, such prototype tools, which are components providing the functionality supporting the activities of energy-aware software development, are described. Links to repositories containing the prototype tools and other software developed are available at the ENTRA project website<sup>1</sup>.

The deliverable includes the following attachments:

- D1.2.1 [LGK<sup>+</sup>16]: Inferring Parametric Energy Consumption Functions at Different Software Levels: ISA vs. LLVM IR. Foundational and Practical Aspects of Resource Analysis. Fourth International Workshop FOPARA 2015, Revised Selected Papers, Lecture Notes in Computer Science, Springer. To appear.

- D1.2.2 [HK16]: Swallow: Building an Energy-Transparent Many-Core Embedded Real-Time System. International Conference on Design, Automation and Test in Europe (DATE 2016), Dresden, Germany, IEEE, March 2016.

- D1.2.3 [HLGL<sup>+</sup>16]: A Transformational Approach to Parametric Accumulated-cost Static Profiling. Thirteenth International Symposium on Functional and Logic Programming (FLOPS 2016), LNCS, Springer, March 2016.

- D1.2.4: *Integrating energy modelling into the development process: A Makefile approach.* Technical brief, December 2015.

http://entraproject.eu/software-and-tools.

## **Contents**

| 1 | Intr | oduction | n e e e e e e e e e e e e e e e e e e e                                     | 3  |

|---|------|----------|-----------------------------------------------------------------------------|----|

| 2 | Ove  | rview of | f the Field of Energy-aware Software Development                            | 5  |

|   | 2.1  | Green    | IT                                                                          | 5  |

|   | 2.2  | Energy   | y-aware software development                                                | 5  |

|   | 2.3  | Motiva   | ation for energy-aware software development                                 | 6  |

|   | 2.4  | Techni   | ques for application software energy efficiency                             | 7  |

|   |      | 2.4.1    | Computational efficiency                                                    | 8  |

|   |      | 2.4.2    | Low-level or intermediate code optimisation                                 | 8  |

|   |      | 2.4.3    | Parallelism                                                                 | 8  |

|   |      | 2.4.4    | Data and communication efficiency                                           | 9  |

|   | 2.5  | Tool su  | apport for energy-aware software development                                | 9  |

| 3 | Soft | ware Er  | ngineering Activities and Scenarios                                         | 11 |

|   | 3.1  | Energy   | y-aware software engineering activities                                     | 11 |

|   |      | 3.1.1    | Specify application, including energy                                       | 12 |

|   |      | 3.1.2    | Construction of energy models                                               | 12 |

|   |      | 3.1.3    | Resource model of deployment platform                                       | 12 |

|   |      | 3.1.4    | Selection of deployment platform                                            | 13 |

|   |      | 3.1.5    | Configure platform                                                          | 13 |

|   |      | 3.1.6    | Design space exploration                                                    | 13 |

|   |      | 3.1.7    | Initial energy profiling                                                    | 13 |

|   |      | 3.1.8    | Detailed energy analysis                                                    | 14 |

|   |      | 3.1.9    | Identify energy bugs                                                        | 14 |

|   |      | 3.1.10   | Energy optimisation or reconfiguring                                        | 14 |

|   |      | 3.1.11   | Verify or certify energy consumption                                        | 14 |

|   | 3.2  | Energy   | y-aware software engineering scenarios                                      | 14 |

|   |      | 3.2.1    | Embedded system development on xCORE                                        | 15 |

|   |      | 3.2.2    | Android app development                                                     | 15 |

| 4 | The  | ENTRA    | A tools front end                                                           | 17 |

| 5 | Ene  | rgy-awa  | are Software Development Tools: Description and Demos                       | 19 |

|   | 5.1  | Multi-l  | level energy analysis and verification tool based on HC IR transformation . | 19 |

|   |      | 5.1.1    | Usage and interface                                                         | 21 |

|    | 5.2   | 2 Multi-level mapper tool                                                           |    |  |

|----|-------|-------------------------------------------------------------------------------------|----|--|

|    | 5.3   | Performing parametric static profiling of energy consumption                        |    |  |

|    | 5.4   | The Swallow platform                                                                | 24 |  |

|    | 5.5   | Optimization via Dynamic Voltage and Frequency Scaling (DVFS) and task              |    |  |

|    |       | scheduling                                                                          | 25 |  |

|    | 5.6   | XMOS tools: Supporting low power design in XC                                       | 26 |  |

|    |       | 5.6.1 Introduction to the interface                                                 | 26 |  |

|    |       | 5.6.2 Combinable                                                                    | 29 |  |

|    |       | 5.6.3 Distributable                                                                 | 30 |  |

|    |       | 5.6.4 Status and use                                                                | 30 |  |

|    | 5.7   | Implicit path enumeration ECSA applications                                         | 30 |  |

|    |       | 5.7.1 Design-space exploration for multi-threaded programs using ECSA               | 31 |  |

|    |       | 5.7.2 Other ECSA applications                                                       | 31 |  |

|    | 5.8   | Tools for Horn clause verification                                                  | 32 |  |

|    | 5.9   | Integrating energy modelling into the development process: A Makefile approach      | 34 |  |

| A  | ENT   | TRA tools front end mini-manual                                                     | 41 |  |

|    | A.1   | User interface                                                                      | 41 |  |

|    | A.2   | Analysis and intermediate version specification                                     | 41 |  |

|    | A.3   | Future versions                                                                     | 42 |  |

| At | tachn | nents                                                                               | 43 |  |

|    | D1.2  | 2.1: Inferring Parametric Energy Consumption Functions at Different Software        |    |  |

|    |       | Levels: ISA vs. LLVM IR                                                             | 45 |  |

|    | D1.2  | 2.2: Swallow: Building an Energy-Transparent Many-Core Embedded Real-Time           |    |  |

|    |       | System                                                                              | 66 |  |

|    | D1.2  | 2.3: A Transformational Approach to Parametric Accumulated-cost Static Profiling    | 73 |  |

|    | D1.2  | 2.4: Integrating energy modelling into the development process: A Makefile approach | 91 |  |

#### 1 Introduction

Deliverable D1.1 gave a preliminary overview of the ENTRA tools supporting energy transparency, in the context of the project's emerging understanding, after two years, of the needs of an energy-aware software development tool-chain. It included a broad description of the kinds of information that energy-aware software engineers needs to know, as well as a summary of the tool support that could provide such information and assist in energy optimization.

In this deliverable we start by reviewing the field of energy-aware software development, identifying the areas most closely related to the ENTRA project, and describing how the field has advanced during the lifetime of the ENTRA project (Section 2).

Then, we describe different activities and scenarios for energy-aware software development (Section 3). In order to demonstrate how the prototype tools and components for analysis, verification and optimisation can be integrated into a tool-chain for energy-aware software development, we have implemented a front-end that provides a friendly Graphical User Interface, that we call the ENTRA tools front end (Section 4). Such components, which provide functionality supporting the activities of energy-aware software development, are described in Section 5.

It is a research challenge in itself, quite apart from the tool functionalities, to consider how they might be integrated into an energy-aware tool-chain. In the ENTRA project we have followed two streams of work:

- 1. Integration in the XC tool-chain, which constitutes the *proof of concept* of the project, where different components, such as the tools (or parts of them) presented in Section 5 can be used, once they are in a mature and stable enough state. Such tools exploit the existing infrastructure of the compiler, intermediate code, and other development tools.

- 2. Stand-alone tool development, which allows a more general investigation and the study of other application areas. This development stream allows the invention of new approaches, the experimentation and evaluation of already developed components, the identification of new components and the investigation of a wider range of scenarios.

The strategy is to migrate tool components from the second stream to the XC tool-chain once they reach a mature enough state (in the longer term). The ENTRA tools front end allows us to experiment with integration of prototype tools with components from the mainstream tool-chain such as the XC compiler and the LLVM framework.

Links to repositories containing the prototype tools and other software developed as part of this deliverable are available at the ENTRA project website<sup>2</sup>.

<sup>&</sup>lt;sup>2</sup>http://entraproject.eu/software-and-tools.

## 2 Overview of the Field of Energy-aware Software Development

In this section we review the field of energy-aware software development, and identify the areas most closely related to the ENTRA project. We also look at how the field has advanced during the lifetime of the ENTRA project.

#### 2.1 Green IT

There has been a growth of interest in the field of *Green IT* [KCWCW10, NKD13, CFS12, NKD13, MA13] since approximately 2010; for example the conference series International Green And Sustainable Computing Conference<sup>3</sup> started in 2011 and the IEEE technical area of Green Computing<sup>4</sup> was launched in 2010. The Energy Aware COmputing workshop series<sup>5</sup> was initiated in Bristol in 2011. Since the start of the ENTRA project in 2012 dedicated workshops such as GREENS<sup>6</sup> and SMARTGREENS<sup>7</sup> have been launched.

Green IT covers energy aspects of the complete life-cycle and context of ICT systems, including software and hardware, development energy costs, maintenance and deployment energy costs, cooling costs, the energy costs of communication infrastructure, raw materials and disposal costs and a host of other energy costs and environmental effects associated directly or indirectly with software systems.

## 2.2 Energy-aware software development

Energy-aware software development is only one aspect of Green IT; it is only concerned with the energy efficiency of software, that is, the energy costs directly attributable to execution of programs. The energy-aware software engineer cannot in general be aware of the whole Green IT field, which involves complex dependencies and tradeoffs.

In short, energy-aware software development concerns the use of tools and methods to allow *energy consumption as a first-class software design goal*. The goal could be to increase energy efficiency or to achieve stated energy targets, for a given ICT application running on a given hardware platform. Energy-awareness for software development thus requires an understanding of the implications for energy consumption of design decisions in the software.

<sup>&</sup>lt;sup>3</sup>http://igsc.eecs.wsu.edu/ (formerly International Green Computing Conference (IGCC))

<sup>4</sup>http://sameekhan.org/tagc/

<sup>&</sup>lt;sup>5</sup>http://www.cs.bris.ac.uk/Research/Micro/eaco.jsp

<sup>6</sup>http://greens.cs.vu.nl/

<sup>&</sup>lt;sup>7</sup>http://www.smartgreens.org/

Very few programmers at present have much idea of how much energy their programs consume, or which parts of the program use the most energy. The development of software tools and techniques for resource-awareness (including energy-awareness) is now attracting more attention, but the field remains somewhat fragmented. Resource analysis is the topic of dedicated workshops such as FOPARA<sup>8</sup>. However, energy modelling is mainly studied in different application contexts such as embedded systems, high-performance systems, mobile systems and so on, rather than as a coherent set of techniques applicable to any software-based system.

The ENTRA project marks itself out from the current state of the art in three main respects.

- It takes a generic approach, not driven by any particular class of applications, platforms or programming languages.

- It combines energy analysis and energy modelling and the interaction between them.

- It considers the tools needed to support energy-aware software development.

#### 2.3 Motivation for energy-aware software development

Environmental impact. The energy consumed by ICT is growing both in absolute terms and as a proportion of the global energy consumption and thus plays an important role in meeting the targets of the Europe 2020 Agenda, which includes a goal to reduce greenhouse gas emissions by at least 20% compared to 1990 levels. Every device, from autonomous sensor systems operating at the mW level to high performance computing (HPC) systems and data centres requiring tens of MWs for operation, consumes a certain amount of energy which results in the emission of CO<sub>2</sub>.

Although energy is ultimately consumed by physical processes in the hardware, the software controls the hardware and indeed typically causes a great deal of energy waste by inefficient use of the hardware. This waste cannot be recovered by relying on the development of more energy-efficient hardware – increasing the energy efficiency of the software is the most effective approach to reducing overall energy consumption.

In many cases the energy efficiency of software has a direct positive effect on the efficiency of other energy-related aspects of systems. Obvious case are cooling costs and battery costs – cooling requirements for data centres are directly related to the power dissipated by the computations, while for mobile systems the number of battery replacements or recharges is similarly reduced if software is more energy-efficient.

<sup>8</sup>http://resourceanalysis.cs.ru.nl/fopara/

**Strategic impact.** The energy efficiency of ICT systems plays a critical role in exploiting the massive amounts of information available in data centres, and the full vision of the so-called Internet of Things. The power requirement of a data centre is typically measured in tens of MW, including cooling costs, while the Internet of Things generates increasing demand for a huge number of very low-power devices. The dream of "wireless sensors everywhere" is accompanied by the nightmare of battery replacement and disposal unless the energy requirements of devices can be lowered to enable them to be powered by energy harvesters or RF power sources.

**Development costs of energy-efficient software.** In the current state of the art, development costs for energy-efficient systems are higher than for energy-wasteful systems due to the extra effort required to take energy consumption into account. This is a significant barrier to making energy efficiency a first-class design goal.

The motivations for ENTRA research in energy-aware software development can thus be summarised as follows.

- 1. To lower the energy costs directly attributable to software execution, helping to reduce the environmental impact of ICT and to enable the next generation of ambient low-power devices.

- 2. To lower energy costs indirectly caused by software, such as the cost of cooling, power supplies, battery replacement and recharging.

- 3. To reduce the costs of the process of developing energy-efficient systems, by developing tools and techniques to assist the energy-aware developer.

## 2.4 Techniques for application software energy efficiency

One of the first works to stress the general importance of software energy efficiency, and identify aspects of software that affect energy consumption, was by Roy and Johnson [RJ97]. Since then the topic has been addressed mostly in the context of specialised application areas such as high-performance computing, embedded systems and mobile systems. There has been some more generic research in the past five years in the context of green computing [Goe13, Dew14, dSCM+12]. However the mainstream view remains that energy efficiency is a concern for hardware designers. Low-power architecture, for example, is still a very active area of research.

ENTRA Deliverable D4.1 [Gal14] summarised a number of software-based approaches to achieving lower energy consumption. Here we briefly review these along with other techniques described in [Lar11, SA12].

#### 2.4.1 Computational efficiency

Firstly, there is a strong correlation between time and energy consumption for a given platform running a single computation thread. There are two reasons for this: less time means fewer instructions and secondly when the task is finished the processor can revert to a lower-power state for the excess time that a less efficient algorithm would use. The latter is called the "race to idle" in [SA12]. The correlation between time and energy is especially strong when asymptotic complexity is considered. It is highly likely, for example, that a single-threaded task that has  $O(n^2)$  time consumption also has  $O(n^2)$  energy consumption. Thus one of the main concerns of the energy-aware programmer, even with no knowledge of the energy consumption of the hardware, is to find computationally efficient algorithms and data structures suited to the task at hand.

#### 2.4.2 Low-level or intermediate code optimisation

Deliverable D4.1 reviewed a range of techniques for low-level code energy optimisations, which could in principle be carried out by a compiler. These range from register allocation policies to avoid overheating a few intensively-used registers, use of VLIW (Very Long Instruction Word) instructions and vectorisation, to exploitation of low-power processor states using frequency and voltage scaling (DVFS). Note that such optimisations, in contrast to computational efficiency, are highly platform-dependent and rely on a platform energy model expressed at the level of low-level code. Computational efficiency as described in Section 2.4.1 is also important in that low-level code optimisations are most effective when applied to frequently executed sections of code, such as tight inner loops, where a small savings in energy can make a significant different to the overall computation.

It was also noted in Deliverable D4.1 that some energy optimisations rely on advanced compile-time (i.e. static) analysis. For example, knowledge of thread load imbalance and knowledge of predictable idle periods when processors can be put into low-power states are difficult to apply in the current compiler state of the art, since the analyses providing this knowledge are still emerging research areas.

#### 2.4.3 Parallelism

The relationship between computational efficiency, time consumption and energy consumption is more complex for parallel than for sequential code. A multithreaded solution using multiple cores is often more energy-efficient than a single-threaded solution, even though the total amount of work done is greater for the multithreaded code, due to the extra instructions needed for

communication and synchronisation. The savings are mainly due to the fact that the overall task time is reduced, and so the processor(s) can revert sooner to a low-power state (the "race to idle" mentioned earlier).

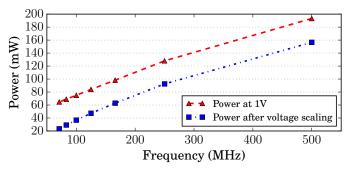

Secondly, there can be energy savings if one or more cores can be run more slowly and still achieve the same overall task time as the sequential code. This is because power (P), frequency (f) and voltage (V) are related by the equation  $P = cV^2f$  where c is a constant. Thus slowing down the processor (reducing f) saves power but not overall energy since the computation time is increased proportionally. However, a lower frequency is typically accompanied by a lower voltage, and the power/energy savings are quadratic in relation to voltage reduction.

#### 2.4.4 Data and communication efficiency

Energy can be saved by minimising data movement. This can be achieved by writing software that reduces data movement by using appropriate data structures, by understanding and exploiting the underlying system's memory hierarchy and by designing multithreaded code that reduces the cost of communication among threads.

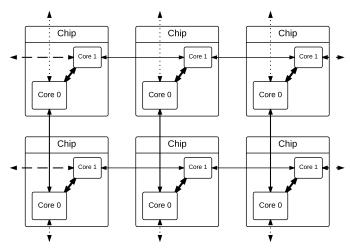

For example the size of blocks read and written to memory and external storage can have a major impact on energy efficiency, while memory layout of compound data structures should match the intended usage in the algorithm, so that consecutively referenced data items are stored adjacently if possible. In multithreaded code, consolidating all read-writes to or from disk to a single thread can reduce disk contention and consequent disk-head thrashing [SA12]. Furthermore, knowledge of the relative communication distances for inter-core communication can be used to place frequently communicating threads close to each other [HK16] thus reducing communication energy costs.

## 2.5 Tool support for energy-aware software development

Given the potential energy optimisations in described above, we identify various classes of tool support for energy-aware software development.

- Tools for energy modelling and transparency through the layers.

- Tool role: to make visible energy consumption associated with programs at different levels.

- Energy mappings showing relation between energy of ISA blocks, intermediate code blocks and source statement blocks.

#### • Energy consumption analysis.

- Tool role: to show how energy models can be used by static analysis to analyse energy consumption.

- Parametric energy expressions derived and displayed (as functions, or as graphs).

Static profiling showing distribution of energy in a program, e.g. highlighting hot blocks.

#### • Energy simulation.

- Tool role: similar to energy analysis tools, but using simulations based on an energy model.

- Components: Simulation-based energy profiling of code, with suitable display of results.

#### • Energy verification.

- Tool role: to show that energy specifications can be checked, and constraints derived giving conditions under which specs are satisfied.

- Display of specifications, and results and interpretation of verification.

- Energy optimization and design space exploration.

- Tool role: to use energy information (from any of the above tools) in manual or automatic (compiler-based) energy optimisation.

- Energy optimising compiler.

- Exploration of thread and communication behaviour with implications for improved design with respect to energy consumption.

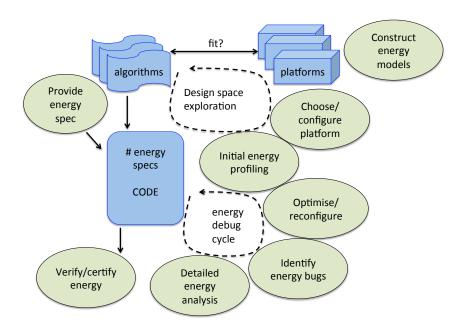

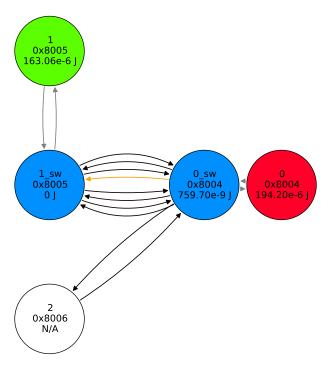

Figure 1: Energy-aware software engineering activities.

## 3 Software Engineering Activities and Scenarios

We now look at energy-aware software from the designer's and developer's point of view. What are the activities that distinguish energy-aware design and development from standard approaches in which energy is considered at the end of the development process, if at all? In Section 3.1 we identify a number of generic activities that play an important role in energy-aware software engineering. In Section 3.2 we make the discussion a little more concrete by sketching scenarios in which these activities are applied.

## 3.1 Energy-aware software engineering activities

In this section we describe the most important activities involved in energy-aware software engineering. Some of these activities are extensions or modifications of conventional software engineering practices; others are new activities that only exist when energy efficiency is a design goal. Figure 1 shows a number of activities and (some of) the inter-dependencies that arise in the context of different scenarios.

#### 3.1.1 Specify application, including energy

The process of developing application software starts with a requirements specification that expresses not only *functional* properties, as in the classical approach, but also *non-functional* properties, including energy consumption and other resources. Classical methods for requirements specification need to be extended to allow non-functional specifications to be expressed.

Satisfying functional properties (in the sense of the classical concept of correctness with respect to a test suite or a formal input-output specification) is as important as doing so for non-functional properties: an application that makes a device run out of batteries before a task is completed is as erroneous and useless as an application that does not compute the right result.

#### 3.1.2 Construction of energy models

Creating energy models for different combinations of hardware platforms and programming languages is a part of the energy-aware development process. At one end of the spectrum, one might expect future hardware manufacturers to deliver an energy model for their instruction set architecture and thus the model would be available "off the shelf". At the other end, some projects might require the construction of an energy model specific to that project, perhaps because the hardware or software environment was not standard. In between these two extremes, energy modelling for energy-aware software development is becoming a more well understood process.

#### 3.1.3 Resource model of deployment platform

If energy efficiency is a design goal, we need to obtain an *energy model of the platform* on which the system is to be deployed (even though the software might be developed on a different platform).

Thus obtaining the appropriate energy model is a vital task in energy-aware software engineering. Not only should an appropriate platform be selected, but its energy model should be available during software development to support other activities (see for example Sections 3.1.6, 3.1.7, 3.1.8 and 3.1.9). We note also that several different energy models for a given platform might be selected, at different levels of abstraction suitable for different activities. For instance, high-level approximate models might be suitable for design space exploration (Section 3.1.6) and initial energy profiling (Section 3.1.7), while more precise low-level models are needed for detailed energy analysis (Section 3.1.8) and optimisation (Section 3.1.10).

#### 3.1.4 Selection of deployment platform

The choice of deployment platform itself might depend on its resource-usage model; thus this activity and Section 3.1.3 are interdependent. By "platform" here is meant both the hardware and the software platform; thus the model should be capable of predicting the energy usage of software (in a given language and with a given runtime environment) being executed on a given piece of hardware.

#### 3.1.5 Configure platform

Some platforms allow configuration that can have implications for energy consumption. Among such settings are clock frequency and voltage, the number of cores and the communication paths among them. At the software level, operating system settings can also be considered, such as the settings for power saving and the resolution of OS timer processes that can send interrupts to other processes.

#### 3.1.6 Design space exploration

Choices taken early on in the design process can have a profound effect on the energy efficiency of the final result. *Design space exploration* as an energy-aware software development activity refers to the process of estimating energy implications of different possible design solutions, before they are implemented. It may involve especially activities such as Selection of deployment platform (Section 3.1.4), Platform configuration (Section 3.1.5) and Initial energy profiling (Section 3.1.7). This involves energy modelling and analysis tools as in some other activities, but with the difference that one is likely to be more satisfied with approximate models and thus rougher estimates of energy consumption rather than precise predictions.

#### 3.1.7 Initial energy profiling

At early stages of energy aware software design and implementation, tools are needed to perform an *initial energy analysis*. The purpose of this is to produce statically an *energy profile* that identifies the overall complexity of the energy consumption of the software and how energy consumption is distributed over the parts of the program. It could also at this stage identify energy bugs (parts of the application software that do not meet their energy consumption specification).

Initial energy analysis requires an an *energy model* of the deployment platform at an appropriate level of abstraction. At early stages, parts of the software may be missing and it might not be possible to compile it to machine instructions; thus an approximate model based on a model of source code might have to suffice.

#### 3.1.8 Detailed energy analysis

During more advanced stages of energy aware software implementation, detailed energy analyses at finer levels of granularity are needed. These are provided by tools containing more precise low-level energy models of the platform, able to give precise estimates of the energy consumption of critical parts of the code, which could be targets for energy optimisation.

#### 3.1.9 Identify energy bugs

Energy bugs occur when software does not conform to an energy specification. The specification might state some overall resource requirement in which energy consumption is implicit, for example on the length of battery life. The bug in such a case could be some energy-consuming process that is more expensive than necessary, a service that is not switched off when required, threads that synchronise badly and spend too much time waiting, and so on.

#### 3.1.10 Energy optimisation or reconfiguring

The broad concept of energy optimisation is applied throughout the whole software engineering process, and starts right at the beginning with design space exploration and selection of appropriate platform, algorithms and data structures.

The specific energy optimisation performed in this activity is driven by the detailed energy analysis and the energy model of the platform. Both manual and automatic optimisations can be applied; the energy analysis should point to the sections of code that use the most energy, either because they involve costly energy operations, or because they are frequently executed (e.g., tight inner loops). This activity also includes application of energy-optimising compilers and such generic optimisers.

#### 3.1.11 Verify or certify energy consumption

Energy-critical applications need to be certified with respect to an energy specification. Tools combining detailed energy models and precise energy analysis are required in order to compare the inferred energy consumption with the specification, either verifying conformance or certifying that it holds within some specified limits of behaviour such as input ranges.

### 3.2 Energy-aware software engineering scenarios

In this section we sketch scenarios in which the activities described in the previous section are applied.

#### 3.2.1 Embedded system development on xCORE

The ENTRA project case studies focussed on embedded systems implemented in the XC language and deployed on the xCORE multicore architecture. An energy-aware software development strategy for such applications might involve the following energy-aware activities.

- Energy specification by writing pragma comments in the XC source code. Such pragmas could express energy constraints derived from customer requirements on the power supply.

- Platform selection and configuration. The xCORE architecture is highly configurable both in terms of the number of cores and their interconnection. The choice and configuration is guided by an energy model applied to proposed solutions, taking into account thread communication energy costs in a given configuration, as described in more detail in Attachment D1.2.2 (Swallow: Building an Energy-Transparent Many-Core Embedded Real-Time System [HK16]).

- Detailed program-independent energy models of the platform at ISA level, are available.

Program-dependent energy models are obtained for XC and LLVM IR code for the application from the ISA model, and used to perform more precise and detailed energy analysis of the application.

- Optimisations of expensive or frequently executed code is performed on the basis of the energy analysis.

- The energy optimising compiler for XC is applied to the application.

- Pragmas in the code are verified using comparison of the energy consumption predicted by the analysis with the constraints in the specification.

#### 3.2.2 Android app development

A case study on Android app energy optimisation was carried out [LG16] (see Attachment D4.2.7 in Deliverable D4.2). The study involved energy modelling and optimisation of applications based on an established game-engine. An energy specification was not given; the aim of the study was to use a source-code-level energy model to identify the most energy-intensive parts of the code in a number of typical use-cases, and then apply manual optimisations, reducing energy usage directly and thus prolonging battery life.

Energy-aware software engineering activities included:

- Building a fine-grained source code energy model by regression analysis from energy measurements on the target hardware and Android software platform of a set of test cases exercising the functions of the underlying game engine.

- Dynamic profiling of the code, which provided an energy profile that allowed the most energy-expensive basic blocks to be identified.

- Manual refactoring of the source code, targeted at the most expensive blocks, which succeeded in increasing energy efficient by a factor of 6% to 50% in various use-case scenarios.

#### 4 The ENTRA tools front end

In order to clarify and demonstrate some of the functionality required to support the energy-aware software development activities described in Section 3.1, we implemented a Java front-end that provides a graphical user interface (the ENTRA tools front end) for some of the prototype tools developed in the ENTRA project. The use of Java allowed tools running on different platforms and operating systems to be provided with a common interface, and prototype tools to be rapidly integrated into the common interface to emphasise their functionality. Note that the ENTRA tools front end does not provide a suitable interface for all the tools, particularly those that are already more closely integrated in the XMOS tool-chain.

A secondary goal of the ENTRA tools front end is to give hints on how the ENTRA prototype tools and components for analysis, verification and optimisation could be integrated into an energy-aware software development tool-chain. The ENTRA tools front end contains tabs corresponding to different tool functions; these can be manually combined to demonstrate tool-chains providing the required functionality supporting energy-aware software engineering activities and scenarios (Section 3).

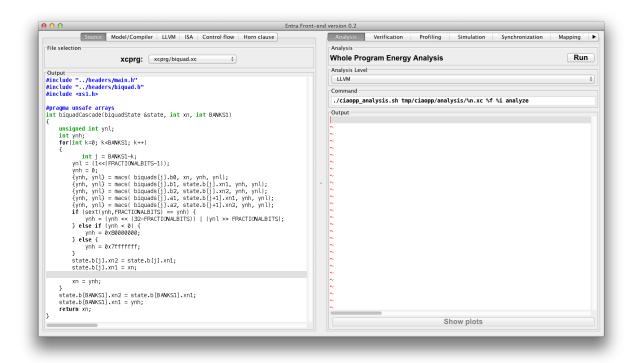

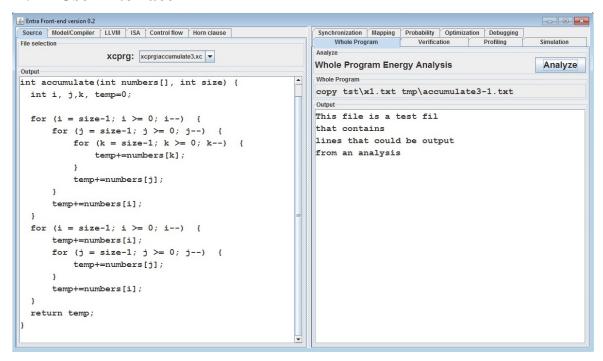

Figure 2: The ENTRA tools front end.

Figure 2 shows a screenshot of the ENTRA tools front end, which has two main sections on

the left and the right. The source file is loaded into the buffer on the left section under the *Source* tab. For demo purposes the user can load one of the benchmarks from the *xcprog* drop down.

The tabs *Analysis* and *Verification* (within the section on the right) are merely indicative of a wide range of functions to which the front end can be adapted. In the two example tabs shown, the user can select the *Analysis Level* to be either *LLVM* or *ISA*, which specify the level (LLVM IR or ISA) to which the XC source is compiled and then analyzed by the underlying tool (e.g., CiaoPP). Once the user presses the button *Run*, the output of the analysis/verification is loaded into the buffer on the right. The underlying command used to invoke the required functionality (e.g., analysis, verification) is also shown under *Command*. The button *Show plots* allows the user to see the output plotted graphically. It is shown using the gnuplot utility.

A short summary of the procedure for integrating a new tool into the ENTRA tools front end is given in Appendix A. The underlying assumption for integration is that the tool with its parameters can be run from the command line. The command line string is incorporated into the Java code and the input and output directed to the appropriate areas of the ENTRA tools front end.

## 5 Energy-aware Software Development Tools: Description and Demos

In this section we describe the final versions of the energy-aware prototype tools (components) for analysis, modelling, verification and optimization developed in the project, that can be integrated to build tool-chains providing the required functionality for the activities and scenarios described in Section 3.

## 5.1 Multi-level energy analysis and verification tool based on HC IR transformation

In this section we describe an experimental prototype tool for analysis and verification of energy, execution time and general resource usage properties.

**Main functionality.** The tool can perform two main kinds of actions:

- Analysis: This action is used to estimate the energy consumed and time spent by the execution of XC programs and each of its procedures (even when there are parts not developed yet). Such information is given in general as functions on some properties of the input data (e.g., range of integers or length of arrays) and can be used by developers of energy-efficient software to make informed design decisions (e.g., redesigning the most energy consuming parts of the programs, using alternative data structures, ...) or optimizing the XC programs, either manually or using a (semi-)automatic optimization tool.

- *Verification*: This action is used to prove whether resource usage specifications are met or not, or to infer conditions under which such specifications are met.

**Input to the tool.** The input to the tool is a file with a program encoded in any of the four following languages: XC source, Instruction Set Architecture (ISA), LLVM Intermediate Representation (LLVM IR), or HC IR. These are recognized by their respective extensions: .xc for XC, .asm for ISA, .ll for LLVM IR, or .pl for HC IR.

For an input file in HC IR format, it is the responsibility of the programmer to include assertions in Internal Assertion Language (IAL) format describing the models for particular resources used for the analysis / verification (see [EG13] for a detailed description of the IAL). Nevertheless, the tool provides some packages for predefined resource models in IAL format. For example, the user can include the package ciaopp (xcore/model/energy) to use the energy model described in D2.2 [EKG14], or the package ciaopp (xcore/model/time) to

use a timing model. For a file in a format different from HC IR (i.e., XC, LLVM IR or ISA), the tool automatically uses the energy and timing models defined by the packages above.

**Output of the tool.** The outcome of the analysis (or the verification) is subsequently included as assertions in the output file in one of the two following formats. For XC, LLVM IR and ISA, the results are formatted in the front end aspect of the Common Assertion Language described in deliverable D2.1 [EG13]. For HC IR the results are formatted in the IAL, i.e., the internal aspect of the Common Assertion Language. The tool also generates graphics of the energy consumption functions involved in the process and the input values for which energy specifications are met, which facilitates the interpretation of the analysis and verification results.

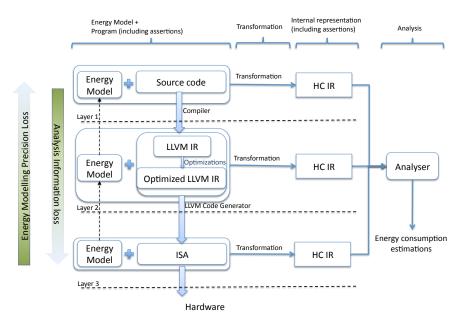

Main features: multi-level analysis, experimental. The tool integrates two different instantiations of the general resource analysis framework described in deliverable D1.1. Both instantiations use energy models defined at the ISA level (see deliverable D2.2 [EKG14]), but one of them performs the analysis at the ISA level (see deliverable D3.1 and [LKS+14]) and the other one performs the analysis at the LLVM IR level [LGK+16] (included in this document as Attachment D1.2.1).

In this sense, the tool is a multi-level analysis and verification tool, and the user can select at which level (LLVM IR or ISA) the analysis is to be performed. In order to perform the analysis at the LLVM IR (resp. ISA) level, the LLVM IR (resp. ISA) corresponding to the input XC file is first generated (by using the standard xcc compiler), and then transformed into HC IR using the LLVM IR (resp. ISA) HC IR translation. The HC IR is then analyzed by the analysis engine. Technical details about such translations can be found in [LGK<sup>+</sup>16] (Attachment D1.2.1).

The selection of the analysis level has an impact on the accuracy of the results and on the class of programs that can be analyzed. Thus, the tool allows experimentation with energy (and time) analysis at different levels of abstraction.

The tool has been integrated in an existing tool-chain for experimentation, the CiaoPP system, leveraging the environment for program analysis, verification, and optimization offered by it, which uses HC IR as internal program representation and is based on modular, incremental abstract interpretation. Functional components from the CiaoPP system can potentially be integrated with a compiler tool-chain, although it may require an implementation effort to make it robust to the real life environment.

#### 5.1.1 Usage and interface

The user can interact with the tool through a Graphical User Interface (GUI) or through a Unix command line. The GUI has mainly used in the project to facilitate experimentation by tool developers and to experiment with aspects of user interaction such as source assertions. We focus here on the command line interface, which has been used for integration in the ENTRA tools front end, in order to demonstrate that it can also be integrated in other tool-chains as well.

The command line interface can be used to perform analysis (and other actions) on XC, LLVM IR and ISA files. The name of the command line executable is ciaopp\_entra and can be used as follows:

```

$ ciaopp_entra [Options] <InputFilename>

```

where <InputFilename>, the last argument, is the path of the input file that contains the program to be processed. The format of this input file is determined by the file name extension (e.g., XC, ISA or HC IR files are recognized by their respective extensions .xc, .asm, .ll, or .pl.). – and [Options] is a space separated sequence of the following possible options:

- The ——analyze option is used to perform the resource usage analysis of the input file.

- The --verify option is used to perform the resource usage *verification* of the input file, by checking the assertions present in the input file. In this case an analysis is first performed as it would be the case if the option were --analyze then the results are compared with the input assertions to be checked.

In case neither the ——analyze nor the ——verify option is specified, no actions (analysis nor verification) are performed on the input file. However, an output file is generated. This behaviour is useful for generating the HC IR representing the ISA or LLVM IR code of the input program.

- The -o <OutputFileName> option specifies that <OutputFileName> is the path of the target output file to be written.

- The --oformat=<OutputFormat> option specifies in which language the output should be written. There are two options for "<OutputFormat>":

- HC IR: the analysis / verification results are written in HC IR.

- source: the analysis / verification results are written in the source language.

- The --level=<level> option determines at which level (LLVM IR or ISA) the analysis is to be performed. For this, the user can set the option to two different values: LLVM or ISA respectively.

- The --req-solver=<solver> option specifies which recurrence equation solver must be used by the resource analysis engine. Currently, the user can set the option to three different values:

- When the option is set to the builtin value (default value), the resource analysis engine uses the builtin solver. This solver is directly incorporated into the CiaoPP analyzer and consequently does not require the installation of any external tool. However, currently, the solver is less powerful than the external solver and therefore can lead to more imprecise analysis results.

- The mathematica value forces the use of Wolfram Mathematica [Mat]. In general, Mathematica is a more powerful recurrence equation solver than the builtin solver, however being an external component, it has to be installed on the machine separately from CiaoPP.

- The chain value forces to use the *chain* strategy from the modular solver implemented in CiaoPP, which basically tries to solve a recurrence relation by calling in sequence each available back-end solver. These back-end solvers are mathematica, builtin, or a specialized solver for recurrences with increasing arguments (that uses ppl). In any case, the first solution found is the one that is returned, obtained from one of the back-end solvers.

- The --math-system=<cas> option specifies which algebraic system must be used by the resource analysis engine to solve operations like simplification of expressions, variable isolation, expression comparison, etc. Currently, the user can set the option to mathematica or builtin (default value).

- The --res-analysis=<analysis> option specifies which analyzer must be used for perform the resource analysis. Currently the options are:

- resources, which forces to use the legacy version of the resource analysis present in CiaoPP.

- res\_plai, indicating that the CiaoPP's abstract interpretation-based resource analysis must be used (default value).

• The --help option displays description of the command line usage including the different options described above.

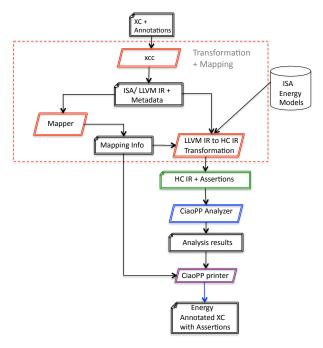

### 5.2 Multi-level mapper tool

In deliverable D3.1, we introduced a novel mapping technique to lift our ISA-level energy model to a higher level, the intermediate representation of the compiler, namely LLVM IR [LA04], implemented within the LLVM tool chain [LLV14]. In deliverable D1.1 under Section 3.2, the mapping tool was introduced, together with a use case example. The mapping techniques implemented by the tool, were evaluated further on both single- and multi-threaded benchmarks, and the results are reported in deliverable D2.3 under Section 2. The evaluation was done using Energy Consumption Static Analysis (ECSA) based on an Implicit Path Enumeration Technique (IPET) [LM95], which we introduced in deliverable D1.1 under Section 4, *Work in Progress*. Our results show that the mapping technique allowed for energy consumption transparency at the LLVM IR level, with accuracy keeping within 1% of ISA-level estimations in most cases. The mapper tool makes energy consumption information accessible directly to the optimizer, and therefore creates new opportunities towards energy specific compiler optimizations.

A paper detailing the mapping techniques together with their evaluation, the ECSA static analysis used and ECSA practical applications at both the ISA and the LLVM IR levels, is attached as D2.3.3 to D2.3.

## 5.3 Performing parametric static profiling of energy consumption

The standard or classical notion of cost (given in terms of different resources, e.g., energy or execution time) inferred by the ENTRA analysers only partially fulfils typical requirements of some energy-aware software development activities. For example, the software developer may want to know which parts of a program are the most resource-consuming and which procedures or functions should be optimised first, because of their greater impact on the overall energy consumption of the main program. Procedures/functions with the highest (standard) costs may not need to be optimised first, but perhaps, procedures/functions with lower costs but which are called many times. In this context, what is really needed, is information about how much of the total cost of a program is each procedure/function responsible for, i.e., the *distribution* of energy consumption over the parts of the program. Such information is provided by the parametric static profiling tool described in [HLGL+16] (also included in this document as Attachment D1.2.3).

The tool analyses a program and produces energy consumption functions giving the *accumulated cost* in selected parts of the program (named *cost centers*) as a function of input data sizes.

Such parameterised information allows to know how the distribution of energy consumption grows depending on the variation of the input, unlike the non-parametric information provided by dynamic profilers. Moreover, the information inferred by the static profiler tool is valid for all input values to the program, in contrast to the information provided by dynamic profilers, which is only valid for particular inputs and execution traces, and hence, may give an incomplete view about the distribution of the energy consumption in the program.

The (accumulated cost) information provided by our static profiling tool can be a more valuable aid for resource-aware software development than standard/classical resource usage analysis as it helps identify parts that should be optimised first. It can provide a ranking of the procedures of the program according to its accumulated cost to guide program optimisation. In addition, such accumulated cost information can be used in combination with functions indicating the number of times each procedure is called (which depend on input data sizes to the main program). These functions can be inferred by specialising the general resource analysis developed in WP3 by defining explicitly a *resource* for the number of calls performed by each cost center procedure. A big complexity order in the number of calls to a procedure (in relation to that of a single call) might give hints to reduce the number of calls to such procedure in order to effectively reduce its impact on the overall energy of the program.

Other situation where the static profiler is useful is when the overall resource complexity of a program might not be obtainable. For instance, some parts of it might be too complex for analysis or else because the code for some parts is not available and the cost cannot even be reasonably estimated. In this case useful information could still be obtained by excluding such parts from the analysis, obtaining information about the resource usage for the rest of the program. We refer to deliverable D3.3 for other aspects of the static profiling tool, such as an overview of the technique behind the tool and other motivations to develop it.

## 5.4 The Swallow platform

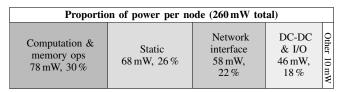

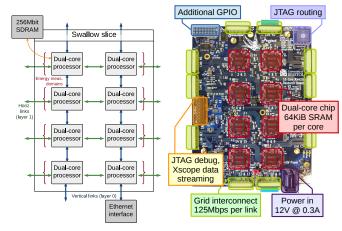

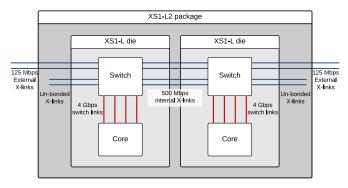

Swallow is an experimental many-core system consisting of XMOS XS1 processors, intended for use as a research tool and to aid the development and testing of software tools and programming techniques in an energy-aware, multi-core context. The system is composed of *slices*, where each slice is a board with sixteen XS1-L cores as a grid arrangement of dual-core chips. Slices can be arranged into a larger grid-like structure, allowing hundreds of cores to be used in a single system.

Although this is a significant leap in the number of cores examined, and goes beyond the limits of the chip vendors development tools, the Swallow system has proved useful in the collection of data for ENTRA related tools. In particular, the rich connectivity of Swallow has aided the

construction of the multi-core model parameters, particularly with respect to the communication costs.

Attachment D1.2.2 is a paper detailing the Swallow platform, including the energy consumption characteristics. This paper will appear at the Design Automation and Test in Europe (DATE) conference 2016 in March. Data from this work has been used in tools from ENTRA, in combination with modelling techniques described in attachment D2.3.1 of Deliverable D2.3.

## 5.5 Optimization via Dynamic Voltage and Frequency Scaling (DVFS) and task scheduling

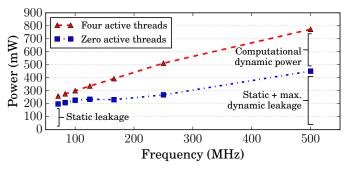

In deliverable D1.1, we introduced an optimization tool that we have developed for solving a general problem of optimal task scheduling in XMOS chips. These XMOS chips are DVFS-enabled multicore systems able to execute multiple threads per core. The set of tasks to be scheduled is represented by its release time, deadline, and estimated power consumption (if available). The tool schedules the tasks in order to find an optimal task-core (thread) assignment, so that all the deadlines are met and the energy consumption is minimised. Based on the way the execution time and power consumption are estimated, a custom genetic algorithm based scheduler is implemented for both stochastic and deterministic scheduling [BLG15]. In addition, we have adapted the well-known YDS algorithm [YDS95], initially designed for DVFS-enabled single core, to a multicore environment for the initial assignment of tasks to cores.

The evaluation of the tool have also been presented in D1.1 under Section 3.4.4 using synthetic data and/or typical power consumption of XMOS chips. The results obtained (reported in [BLG13, BLG15]) confirm the potential of energy-aware scheduling coupled with DVFS for optimising energy consumption.

Further advancements have been reported in [?] and [?]. In [?], an approach to scheduling problems based on a custom evolutionary algorithm (EA) is described. The algorithm is fed with information provided by the CiaoPP static analyzer about predictions of the energy consumed by tasks. The speed ups gained using static analysis predictions solve the time inefficiency problem faced by EAs. In cases when our custom EA fails to produce a feasible solution, our approach resort to a modified YDS algorithm, which is an adaptation to multicore environments and to situations when the static power becomes the predominant part. This combined approach (custom EA algorithm with modified YDS) produces an energy efficient scheduling in reasonable time, that always finds a viable solution. Our approach has been tested on multicore XMOS chips in different scenarios, and the experimental results show that the modified YDS algorithm improves the original one up to 20%, while the custom EA can save 55 - 90% more energy on average than the modified YDS.

In [?], a trade-off between accuracy and energy is studied for the problem of energy efficient scheduling and allocation of tasks in multicore environments, where the tasks can permit certain loss in accuracy of either final or intermediate results while still providing proper functionality. Such situations allow the application of techniques that decrease the computational load, which result in significant energy savings but also in certain accuracy loss. In particular, we have applied the loop perforation [?] technique that transforms loops to execute a subset of their iterations. The experiments conducted on a case study in different scenarios show that our new scheduler enhanced with loop perforation improves the previous one, achieving significant energy savings (31% on average) for acceptable levels of accuracy loss.

#### 5.6 XMOS tools: Supporting low power design in XC

The XMOS tools 14.1 include a global optimiser and an implementation of interfaces; the latter (described in deliverable D4.2) to enable modular development of software in an energy efficient matter, the former, described in this section, to generally increase efficiency of applications.

The XMOS programming environment, centered around the XC programming language, requires a program to be split into tasks that communicate over channels.

Although this model can naturally support low energy programs by enabling the programmer to spread their load over devices that run at similar low frequencies, the process of splitting tasks and balancing them is one that can be at odds with normal software engineering practices, where software is split in modules that are based on their function, not on their load balancing properties.

To this effect, we have developed an extension to the XC language, the *interface*, that enables software to be split functionally, yet still achieve load balancing as is needed to develop a low-energy design.

#### **5.6.1** Introduction to the interface

The idea behind the interface is to merge the traditional concept of a software module in an imperative language, with the concept of threads communicating over channels.

When programming using an interface, there are at least two actors: a *server* and one or more *clients*. The server implements the interface, and the client makes calls to the interface. Notionally, the server runs in a separate thread to the client, and a channel connects the two. This model is similar to that of an RPC (Remote Procedure Call), or to forms of distributed Object Oriented programming models.

An example interface is shown below:

This definition states that there are four calls that a client can make to a server: write, read, send\_stop\_bit, and shutdown. The server side of the interface implements those four calls, and the client side to the interface can make those calls. The calls themselves happen, under the bonnet, over channels.

For a server with a single client the server side of the interface is implemented as follows:

}

The client can make calls i2c\_server.send\_stop\_bit() akin to an object oriented programming model. Multiple clients are also supported by using an array of channels. In this particular example, a client can choose to make an atomic sequence of calls, which leads to a rather complex case statement:

```

void i2c_master(server interface i2c_master_if c[n], size_t n,

port p_scl, port p_sda, unsigned kb_per_sec) {

unsigned bit_time = (XS1_TIMER_MHZ * 1000) / kb_per_sec;

unsigned locked_client = -1;

p_scl :> void;

p_sda :> void;

while (1) {

select {

case (size_t i =0; i < n; i++)

(n==1 || locked_client == -1 || i == locked_client) =>

c[i].read(uint8_t device, uint8_t buf[m], size_t m,

int send_stop_bit) -> i2c_res_t result:

locked_client = send_stop_bit ? -1 : i;

result = (ack == 0) ? I2C_ACK : I2C_NACK;

break;

case c[int i].send_stop_bit(void):

locked\_client = -1;

break;

. . .

}

}

}

```

Here, locked\_client is a variable that stores the client that is currently in an atomic sequence of reads and or writes. There are two ways that the sequence can end: by a call to read() with send\_stop\_bit set, or by a call to send\_stop\_bit().

Analysing the first case statement reveals how the multiple interfaces work:

```

case (size_t i =0; i < n; i++)

(n==1 || locked_client == -1 || i == locked_client) =>

c[i].read(...

```

That is short-hand for a series of n case statements on c[0]...c[n-1] with each case having a guard that the case statement can only occur if at least one of three conditions is met:

- 1. n==1 (there is only one client nobody else could have started an atomic sequence that is being interrupted) or

- 2. locked\_client == -1 (no atomic sequence has started) or

- 3. i == locked\_client (it is this client who is running an atomic sequence)

This description is hence a complete generic description, that works for any number of clients needing access to this single interface.

If there is only a single client, it may seem that the former implementation of the server is more efficient; however, the global optimiser (developed in WP4), actually makes the implementations as efficient. If only a single client is used, then the call to  $i2c\_master$  will use the value 1 for n, and as there will only be one call the function  $i2c\_master$  will be specialised for the case where n equals 1. This specialisation will throw away all the guards (as the condition n==1 evaluates to true), and will subsequently throw away  $locked\_client$  since it is no longer used.

#### 5.6.2 Combinable

One common problem is that often tasks can be described as individual threads, but implementing them as a single thread is energy inefficient, as the thread will be under-utilised: best energy efficiency is obtained by balancing all threads.

For this purpose, we have defined the <code>[[combinable]]</code> attribute. Functions marked <code>[[combinable]]</code> can be merged together and implemented in a single thread by the toolchain. When a function is marked as <code>[[combinable]]</code> it must be implemented using the following template:

```

[[combinable]]

void ...(server interface c, ...) {

...

while (1) {

select {

```

The programmer using the module can decide on whether and how to combine different combinable servers, by placing all the servers in a single thread. This loads that one thread more heavily, but reduces the total number of threads required, reducing energy load.

#### 5.6.3 Distributable

The opposite of a [[combinable]] interface is a [[distributable]] interface; that is an interface where the server is so simple that it can be assimilated in the client(s) side. This is another way to balance load and thereby reduce energy.

#### 5.6.4 Status and use

Interfaces have been released during the project in version 13 of the tools; and subsequent optimisations in version 14 of the tools.

Where appropriate, software libraries have been rewritten to make use of interfaces, simplifying modularisation and software development.

Compared to the pre-interface status; modularised software engineering principles can now be applied to a programming model that supports energy efficient design.

### 5.7 Implicit path enumeration ECSA applications

In this section we provide a set of ECSA applications. Software developers, compiler engineers, development tools and RTOS can get advantage of these applications for making energy aware decisions. ECSA using the Implicit Path Enumeration Technique (IPET) was introduced in D1.1 under section 4.1 and used together with the high level energy model as described in D2.3 under Section 2. A paper detailing the ECSA techniques together with its practical applications is attached as D2.3.3 to D2.3.

#### 5.7.1 Design-space exploration for multi-threaded programs using ECSA

ECSA is applied to a set of multi-threaded programs for the first time to our knowledge. This is a significant step beyond existing work that examines single-thread programs, because such an analysis can provide significant guidance for time-energy design space exploration between different numbers of threads and cores.

The first class of parallel programs to which ECSA was applied is the class of replicated non-communicating threads. The user can make energy aware decisions on the number of threads to use, with respect to time and energy estimations retrieved by our analysis. For example, take four independent matrix multiplications on four pairs of equally sized matrices  $(28 \times 28)$ . Our analysis will show that a single thread will have an execution time of 4x the time needed to execute one matrix multiplication. However, two threads will half the execution time and decrease the energy by 54%. Four threads which will half the execution time again, and decrease the energy by 41% compared to the two-thread version. Using more threads increases the power dissipation, but the reduction in execution time saves energy on the platform under investigation. Although there is a different estimation error between different numbers of active threads, the error range of 6% is small enough to allow comparison between these different versions.

The second class of parallel programs that our ECSA was applied to was streaming pipelines of communicating threads. There is a choice in how to spread the computation across threads to maximize throughput and therefore minimize execution time or lower the necessary device operating frequency. Having a number of available threads, a number of cores and the ability to apply voltage and frequency scaling, provides a wide range of configuration options in the design phase, with multiple optimization targets. This can range from optimizing for quality of service, time and energy, or a combination of all three. Our ECSA can take advantage of the fact that the energy model used can be parametric to voltage and frequency, to statically identify the most energy efficient configuration of the same program, among a number of different options that deliver the same required performance. The first step of analyzing the pipelined versions of industrial filter applications has been made. We are currently working on extending our ECSA to automatically exploit the possible different configurations and provide the optimal solution, within the user's constraints.

#### 5.7.2 Other ECSA applications

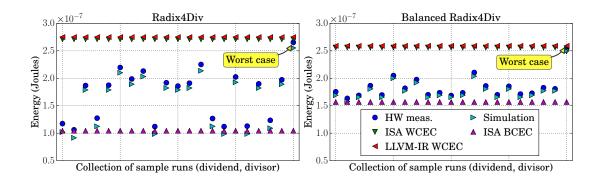

Figure 3 shows the ISA energy consumption upper and lower bounds retrieved by ECSA for the Radix4Div and B.Radix4Div benchmarks. Radix4Div benchmark is a radix-4 software divider and B.Radix4Div is a less efficient version which is added for comparison. This version omits an early return when the dividend is greater than 255. A consequence of excluding this

Figure 3: Radix4 division benchmark ECSA estimations across all test cases.

optimization is that CFG paths become more balanced, with less variation between the possible execution paths. The effect of this modification can be seen in Figure 3. In the optimized version, the energy consumption across different test cases varies significantly, creating a large range between the upper and lower energy consumption bounds. Conversely, the unoptimized version shows a lower variation, thus narrowing the margin between the upper and lower bounds, but has a higher average energy consumption. Knowledge of such energy consumption behavior can be of value for applications like cryptography, where the power profile of systems can be monitored to reveal sensitive information in side channel attacks. In these situations, ECSA analysis can help code developers to design code with low energy consumption variation, so that any potential leak of information that could be obtained from power monitoring can be obfuscated.

#### 5.8 Tools for Horn clause verification

Constrained Horn clauses (CHCs) are intermediate representations suitable for expressing the semantics of a variety of programming languages and computational models. As a result, they have become a popular formalism for verification [BGMR15, GK14]; attracting both the logic programming and software verification communities [BFRS14]. Several verification techniques and tools have been developed for CHCs, among others, SeaHorn [GKKN15], QARMC [GLPR12], VeriMap [DAFPP14], Convex polyhedral analyser [KG15], TRACER [JMNS12], ELDARICA [HKG $^+$ 12],  $\mu Z$  [HBdM11] and Trace abstraction refinement tool [WJ15].

The ENTRA project has adopted (constrained) Horn clauses as an internal representation capable of representing source code, LLVM IR and ISA. The CiaoPP system incorporates Horn clause analysis tools, including a generic framework for resource analysis (see Section 5.1). The tools described in this section are development intended to extend and strengthen these tools. We present them here as stand-along tools operating on Horn clauses; in their intended application

the Horn clauses are derived from the application which is under (energy-aware) development.

State-of-the-art Horn clause verification tools verify functional properties of programs (properties relating program variables); they can also be used to verify non-functional properties like *energy* if we instrument programs (clauses) with energy counters.

**Energy-instrumented clauses** Let P be a set of CHCs and  $P_{en}$  be a set of CHC constructed as follows.

- For each predicate p of arity m define a predicate p' of arity m+1.

- For each clause in P of the form

$$p(X) \leftarrow \phi, p_1(X_1), \dots, p_n(X_n)$$

we have a clause

$$p'(X, K) \leftarrow \phi, p'_1(X_1, K_1), \dots, p'_n(X_n, K_n), K = K_1 + \dots + K_n$$

in  $P_{en}$ , where  $K_1, \ldots, K_n, K$  are energy variables added as the final argument for their respective predicates.

Energy forms a part of a program with program instrumentation, which allows the use of above mentioned tools to verify properties relating program's input variables (equivalently other variables) with its energy consumption.

During the ENTRA project, we have developed two Horn clause verification tools (for verifying functional properties, and thus energy properties via instrumentation), namely,

- RAHFT $^9$ ;

- LHornSolver<sup>10</sup>.

Both of these tools are based on the *abstraction-refinement* scheme, but the second one only uses a linear Horn clause solver for solving non-linear Horn clauses, potentially allowed greater scalability. These tools are also able to produce witnesses showing that a property is satisfied or violated, in contrast to other resource analysis tools in the literature, including CiaoPP. Properties are represented as integrity constraints on the Horn clauses, which are easily expressed as assertions in the CiaoPP assertion language.

<sup>&</sup>lt;sup>9</sup>available from https://github.com/bishoksan/RAHFT

$<sup>^{10}</sup>$ available from https://github.com/bishoksan/LHornSolver

**Usage.** The tools are all command-line runnable, taking a Horn clause file as input and generating various kinds of output file, containing invariants for each predicate, checks on the satisfaction of integrity constraints and counterexamples if such constraints are violated.

The tools use as backends powerful solvers such as the Parma Polyhedra Library [BHZ08] and the Yices SMT solver [Dut14], which need to be installed to run the tools.

## 5.9 Integrating energy modelling into the development process: A Makefile approach

This tool serves to demonstrate how the Instruction Set Simulation (ISS) modelling tools, and associated energy model that underpins much of the work used in ENTRA, can be integrated directly into the software development process.

The output of the research effort is described in more detail in Deliverable D2.3 and its predecessor, D2.2. In this deliverable, attachment D1.2.4 is a technical brief that gives a demonstration of the integration of the tools used in these works. The motivation behind the approach of the tool, is that the vendor's existing tools are Makefile based, therefore it is intuitive in enable energy modelling as part of this process.

A number of software components are required, some of which were developed during the project, whilst others are supporting libraries. These are listed in attachment D1.2.4. An example, based on the FIR filter code from work package 5, is used in the technical brief. The tool is principally command-line based, but also has the facility to display modelling results graphically. In the example, this is done via the default PDF viewer of the user's desktop environment, although this could be integrated into any other graphical tool.

The code for the tools has been provided to the project, so that it can be made available in an appropriate manner.

## References

- [BFRS14] Nikolaj Bjørner, Fabio Fioravanti, Andrey Rybalchenko, and Valerio Senni, editors. *Proceedings First Workshop on Horn Clauses for Verification and Synthesis, HCVS 2014, Vienna, Austria, 17 July 2014*, volume 169 of *EPTCS*, 2014.

- [BGMR15] Nikolaj Bjørner, Arie Gurfinkel, Kenneth L. McMillan, and Andrey Rybalchenko. Horn clause solvers for program verification. In Lev D. Beklemishev, Andreas Blass, Nachum Dershowitz, Bernd Finkbeiner, and Wolfram Schulte, editors, Fields of Logic and Computation II Essays Dedicated to Yuri Gurevich on the Occasion of His 75th Birthday, volume 9300 of Lecture Notes in Computer Science, pages 24–51. Springer, 2015.

- [BHZ08] R. Bagnara, P. M. Hill, and E. Zaffanella. The Parma Polyhedra Library: Toward a complete set of numerical abstractions for the analysis and verification of hardware and software systems. *Science of Computer Programming*, 72(1–2):3–21, 2008.

- [BLG13] Z. Banković and P. Lopez-Garcia. Genetic Algorithm-based Allocation and Scheduling for Voltage and Frequency Scalable XMOS Chips. In *Hybrid Artificial Intelligent Systems (HAIS 2013)*, volume 8073 of *Lecture Notes in Computer Science*, pages 401–410. Springer, 2013.

- [BLG15] Zorana Banković and Pedro Lopez-Garcia. Stochastic vs. Deterministic Evolutionary Algorithm-based Allocation and Scheduling for XMOS Chips. *Neuro-computing*, 150:82–89, February 2015.

- [CFS12] Eugenio Capra, Chiara Francalanci, and Sandra Slaughter. Is software "green"? application development environments and energy efficiency in open source applications. *Information & Software Technology*, 54(1):60–71, 2012.

- [DAFPP14] Emanuele De Angelis, Fabio Fioravanti, Alberto Pettorossi, and Maurizio Proietti. Verimap: A tool for verifying programs through transformations. In Erika Ábrahám and Klaus Havelund, editors, *TACAS*, volume 8413 of *Lecture Notes in Computer Science*, pages 568–574. Springer, 2014.

- [Dew14] Robert Dewor. Energy efficiency of web applications. Master's thesis, Faculty of Economics, 2014.

- [dSCM+12] Clauirton de Siebra, Paulo Costa, Regina C. G. Miranda, Fabio Q. B. da Silva, and André Luis M. Santos. The software perspective for energy-efficient mobile applications development. In Eric Pardede and David Taniar, editors, *The 10th International Conference on Advances in Mobile Computing & Multimedia, MoMM '12, Bali, Indonesia December 03 05, 2012*, pages 143–150. ACM, 2012.

- [Dut14] Bruno Dutertre. Yices 2.2. In Armin Biere and Roderick Bloem, editors, Computer-Aided Verification (CAV'2014), volume 8559 of Lecture Notes in Computer Science, pages 737–744. Springer, July 2014.

- [EG13] K. Eder and N. Grech, editors. *Common Assertion Language*. ENTRA Project: Whole-Systems Energy Transparency (FET project 318337), November 2013. Deliverable 2.1, http://entraproject.eu.

- [EKG14] K. Eder, S. Kerrison, and K. Georgiou, editors. *Low-Level Energy Models*. ENTRA Project: Whole-Systems Energy Transparency (FET project 318337), May 2014. Deliverable 2.2, http://entraproject.eu.

- [Gal14] J.P. Gallagher, editor. *Energy Optimization: Basic Static Techniques*. ENTRA Project: Whole-Systems Energy Transparency (FET project 318337), August 2014. Deliverable 4.1, http://entraproject.eu.

- [GK14] John P. Gallagher and Bishoksan Kafle. Analysis and transformation tools for constrained Horn clause verification. *TPLP*, 14(4-5 (additional materials in online edition)):90–101, 2014.

- [GKKN15] Arie Gurfinkel, Temesghen Kahsai, Anvesh Komuravelli, and Jorge A. Navas. The seahorn verification framework. In Daniel Kroening and Corina S. Pasareanu, editors, *Computer Aided Verification 27th International Conference, CAV 2015, San Francisco, CA, USA, July 18-24, 2015, Proceedings, Part I*, volume 9206 of *Lecture Notes in Computer Science*, pages 343–361. Springer, 2015.

- [GLPR12] Sergey Grebenshchikov, Nuno P. Lopes, Corneliu Popeea, and Andrey Rybalchenko. Synthesizing software verifiers from proof rules. In Jan Vitek, Haibo Lin, and Frank Tip, editors, *ACM SIGPLAN Conference on Programming Language Design and Implementation, PLDI '12, Beijing, China June 11 16, 2012*, pages 405–416. ACM, 2012.

- [Goe13] Fethullah Goekkus. Energy efficient programming: an overview of problems, solutions and methodologies. Technical report, University of Zurich, 2013.