# **ENTRA**

318337

**Whole-Systems ENergy TRAnsparency**

# **High-Level Energy Models**

Deliverable number: D2.3

Work package: Energy Modelling Through the System Layers (WP2)

Delivery date: 1 July 2015 (33 months)

Actual date: 11 September 2015 (revised 01.03.2016)

Nature: Report

Dissemination level: PU

Lead beneficiary: University of Bristol

Partners contributed: Roskilde University, University of Bristol, IMDEA Software Insti-

tute, XMOS Limited

Project funded by the European Union under the Seventh Framework Programme, FP7-ICT-2011-8 FET Proactive call.

### **Short description:**

This deliverable presents energy models that apply higher levels of abstractions or new levels of information and detail, building upon the work conducted earlier in the project and previously presented in D2.1. The work herein comprises extensions into several areas, each of which provides new dimensions for further design space exploration by software developers. It feeds into several tasks of other work packages, namely energy aware tools (T1.1) in energy-aware software engineering (WP1), along with energy and quality trade-offs (T4.2) and energy aware scheduling (T4.3) in optimization (WP4).

There are four main topics that this deliverable contributes to: energy modelling at the intermediate representation used during code compilation, multi-core communication modelling, worst case data-aware energy modelling, and modelling of application source code.

This deliverable includes the following attachments:

- D2.3.1. *Modelling software energy consumption in a multi-core network of embedded multi-threaded processors.* In preparation for conference submission.

- D2.3.2. Data dependent energy modelling: A worst case perspective. In preparation for conference submission.

- D2.3.3. On the Value and Limits of Multi-level Energy Consumption Static Analysis for Deeply Embedded Single and Multi-threaded Programs. arXiv preprint arXiv:1510.07095, 2015.

- D2.3.4. *On the infeasibility of analysing worst-case dynamic energy.* To be submitted to the ACM Journal of Transactions on Embedded Computing (TECS).

# **Contents**

| 1  | Intr  | roduction                                                                     |    | 3 |

|----|-------|-------------------------------------------------------------------------------|----|---|

| 2  | Ene   | rgy modelling at the LLVM IR level                                            |    | 4 |

|    | 2.1   | Benchmarks and results                                                        |    | 5 |

|    | 2.2   | LLVM IR analysis accuracy                                                     |    | 7 |

|    | 2.3   | LLVM IR level ECSA applications                                               |    | 7 |

|    | 2.4   | Related publications and dissemination                                        |    | 8 |

| 3  | Mul   | ti-core modelling with communication costs                                    |    | 9 |

|    | 3.1   | Improved core energy model                                                    |    | 9 |

|    | 3.2   | VFS energy consumption modelling                                              |    | 9 |

|    | 3.3   | Multi-core energy consumption and communication                               | 1  | 0 |

|    | 3.4   | Dissemination                                                                 | 1  | 1 |

| 4  | Wor   | est case energy and defining data-aware energy models                         | 1  | 2 |

| 5  | Ene   | rgy modelling of application source code                                      | 1  | 3 |

|    | 5.1   | Introduction and Motivation                                                   | 1  | 3 |

|    |       | 5.1.1 An experiment in source-code energy modelling                           | 1  | 4 |

|    | 5.2   | Code to Energy                                                                | 1  | 4 |

|    |       | 5.2.1 Block Division                                                          | 1  | 4 |

|    |       | 5.2.2 Basic Energy Operations                                                 | 1  | 6 |

|    |       | 5.2.3 Data Collection                                                         | 1  | 6 |

|    |       | 5.2.4 Power Tracing & Model                                                   | 1  | 7 |

|    | 5.3   | Experiment Setup                                                              | 1  | 7 |

|    |       | 5.3.1 Target & Power Measurement                                              | 1  | 7 |

|    |       | 5.3.2 Source Code & Case Design                                               | 1  | 8 |

|    | 5.4   | Model Construction                                                            |    | 8 |

|    | 5.5   | Preliminary Results (Inference Accuracy)                                      | 2  | 0 |

|    | 5.6   | Dissemination                                                                 | 2  | 2 |

| At | tachr | ments                                                                         | 2  | 7 |

|    | D2.3  | 3.1: Modelling software energy consumption in a multi-core network of embedde | ed |   |

|    |       | multi-threaded processors                                                     | 2  | 9 |

|    | D2.3  | 3.2: Data dependent energy modelling: A worst case perspective                | 4  | 0 |

| D2.3.3: On the Value and Limits of Multi-level Energy Consumption Static Analysis |    |

|-----------------------------------------------------------------------------------|----|

| for Deeply Embedded Single and Multi-threaded Programs                            | 50 |

| D2.3.4: On the infeasibility of analysing worst-case dynamic energy               | 80 |

### 1 Introduction

The ENTRA project strives to communicate energy consumption data through the many layers of abstraction that are present in the engineering of modern embedded systems. The previous deliverable from work package 2, D2.2, presented low-level energy modelling techniques, that could be used to inform analysis tools, potentially directed by the common assertion language defined in deliverable D2.1. This deliverable extends the modelling upwards, into higher levels of abstraction, as well as looking at new parameters that can aid design space exploration.

Several areas of work have contributed to achieving this. The accuracy of higher level modelling and analysis is often dependent upon the accuracy of the underlying models, so refinements to low-level models and simulators have been made in order to improve the foundational aspects of this work. The parametrisation of models has also been broadened, in order to explore opportunities for wider ranging design exploration, as well as the potential to define more detailed bounds that can be used for example with the common assertion language. These include data-dependent energy modelling, where the data values processed by a device have an influence on the energy consumption, not just the instructions (Section 4), and voltage frequency scaling (VFS) parameters that can be applied to processors to constrain performance whilst reducing power (Section 3).

Three higher level approaches are detailed. The first (Section 2) demonstrates and evaluates an application of a mapping from the LLVM compiler's Intermediate Representation (IR) to the low level energy model of a processor's Instruction Set Architecture (ISA). The second approach extends our core energy modelling efforts to multiple networked cores (Section 3), with new simulation improvements as well as higher level modelling and visualisation of energy consumption. Finally, we propose a new method for modelling energy consumption at application source code level, specifically for software targeting the Android Operating System (Section 5).

# 2 Energy modelling at the LLVM IR level

In deliverable D3.1, we introduced a novel mapping technique to lift our ISA-level energy model to a higher level, the intermediate representation of the compiler, namely LLVM IR [LA04], implemented within the LLVM tool chain [LLV14]. This enables Energy Consumption Static Analysis (ECSA) to be performed at a higher level than Instruction Set Architecture (ISA), thus introducing energy transparency into the compiler tool chain by making energy consumption information accessible directly to the optimizer.

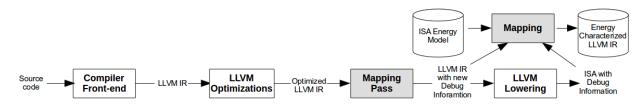

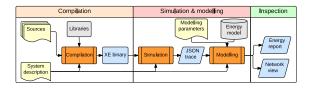

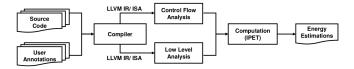

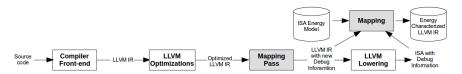

Figure 1: Overview of the mapping process.

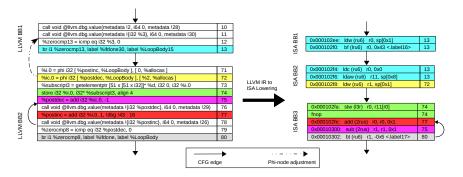

A prototype version of a mapping tool implementing the mapping techniques was described in Deliverable D1.1. An overview of this tool is given in Figure 1. Our mapping pass is introduced into the compilation process after LLVM optimizations to tag each LLVM IR instruction with a unique debug location. The mapping phase runs after the LLVM lowering phase and maps LLVM IR instructions with the new debug locations to the emitted ISA instructions. The ISA energy model is then used to accumulate the energy value of each LLVM IR instruction based on its mapped ISA instructions. This technique was further calibrated and evaluated using a set of single- and multi-threaded benchmarks, mainly selected from a number of industrial embedded applications. For the evaluation we performed ECSA based on two techniques.

The first ECSA technique is based on setting up a system of recursive cost equations over a program P that capture its cost (energy consumption) as a function of the sizes of its input arguments. This work has been performed for single threaded benchmarks and the results were presented in deliverable D3.2 (Attachment D3.2.4) as well as in deliverable D1.1 and integrated into CiaoPP tool. An improved version of this work has been accepted for publication [LGK<sup>+</sup>15]. This work studies the ECSA analysis at different levels (ISA vs. LLVM IR), the results show that LLVM IR level analysis using mapping techniques to lift an ISA model to LLVM IR level is a good compromise since 1) much of the program information (e.g. types) is available at LLVM IR level, unlike at ISA level, allowing analysis of bigger class of programs, and 2) the analysis performed at either level is reasonably accurate and the relative error between the two analyses at different levels is small. ISA-level estimations are slightly more accurate than the ones at the

LLVM IR level (3.9% vs. 6.4% error on average with respect to the actual energy consumption measured on the hardware, respectively).

The second ECSA technique is based on Implicit Path Enumeration Technique (IPET) [LM95] and performed for both single- and multi-threaded benchmarks, which we introduced in deliverable D1.1 under Section 4, *Work in Progress*. Our results show that the mapping technique allowed for energy consumption transparency at the LLVM IR level, with accuracy keeping within 1% of ISA-level estimations in most cases. The rest of this section provides an evaluation of this technique.

### 2.1 Benchmarks and results

Our objective is to calibrate and evaluate the effectiveness of our mapping technique on common industrial, deeply embedded applications. Table 1 summarizes all of the benchmarks' attributes. The meaning of the columns is as follows: *Source* indicates where the benchmark was obtained, *Description* provides insight into the benchmarks' functionality, *NCSL* is the number of noncommentary source lines of code, T is the number of threads used, and the remaining columns indicate the presence of loops (L), nested loops (N), arrays and/or matrices (A), bitwise operations (B), a complex CFG structure (CP), multiple functions (MF) and thread communications (C).

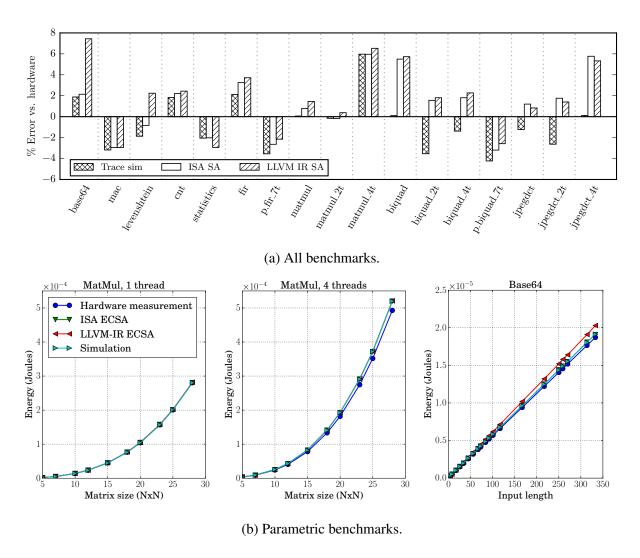

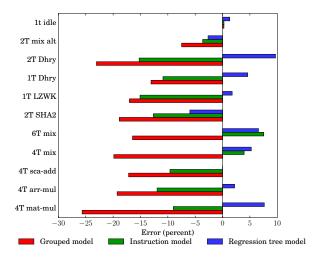

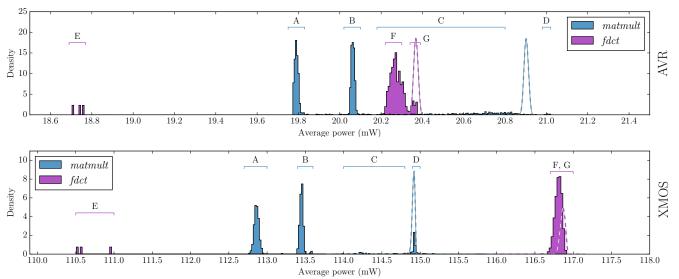

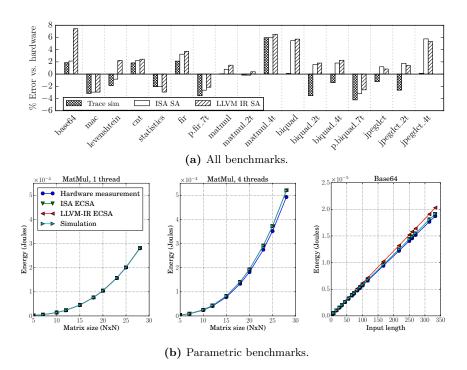

To do so, three analysis techniques were compared to hardware energy measurements for our benchmarks. Figure 2a presents the error margin of ISA energy model combined with the three analysis techniques compared to hardware energy measurements for our benchmarks. Trace Sim produces instruction traces from simulation, ISA ECSA uses the model for static analysis at the ISA level and LLVM IR ECSA uses our mapping technique to apply the model and analysis at LLVM IR level. For all benchmarks with multiple test parameters, the geometric mean of the errors is used. Figure 2b compares energy estimates to hardware measurements for a range of parameters in three appropriate benchmarks. Benchmarks were compiled with xcc version 12 [XMO14] at optimization level O2, which is the default for most compilers.

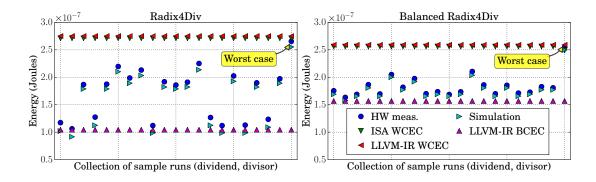

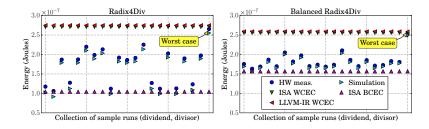

For the software division and floating point benchmarks, ECSA provides a constant energy consumption across all test cases, as they contain no loops that are directly affected by the functions' arguments. Figure 3 demonstrates this for Radix4Div and B. Radix4Div. Considering that IPET is intended to provide bounds based on a given cost model, in our case it tries to select the worst case execution paths in terms of the energy consumption, and therefore ECSA estimations seen in Figure 3 represent a loose upper bound on the energy consumption of each benchmark. Similar figures were also retrieved for the two SoftFloat benchmarks. These bounds in most cases can not be considered safe, as they might be undermined by the use of a non data sensitive energy model and analysis. However, they can still give the application

Figure 2: Hardware measurements compared to ECSA and ISA trace estimation.

Figure 3: Results for benchmarks with constant ECSA estimations across all test cases.

programmer valuable guidance towards energy aware software development in the absence of energy measurements.

Generally, for all results shown here a proportion of error is present in both forms of static analysis as well as simulation based energy modelling. The error in the simulation based model is a baseline for the best achievable error in static analysis, as simulation has more accurate execution information available to it. For all the benchmarks, the ISA ECSA results are overapproximating the trace based energy estimations. This applies also to the LLVM IR ECSA results with exception of the statistics benchmark. This over-approximation is a product of the bound analysis used which is trying to select the most energy costly CFG path based on the provided cost model. A smaller difference between the results of the ISA ECSA results and the trace based energy estimations indicates that the execution path selected by the IPET fits better the actual execution path of a benchmark than LLVM IR ECSA.

## 2.2 LLVM IR analysis accuracy

This form of analysis is solely dependent on the accuracy of the mapping technique. As can been seen in Figure 2a, for all benchmarks the LLVM IR ECSA results are within one percentage point error of ISA ECSA results, except for Base64 benchmark with a further 5.3 percentage points error. In this case the CFGs of the two levels were significantly different due to basic blocks introduced from branches in the ISA level CFG. This is one of the few cases where the mapper was unable to accurately track the differences between the two CFGs.

## 2.3 LLVM IR level ECSA applications

Our LLVM IR analysis results demonstrate a high accuracy with a deviation in the range of 1% from the ISA ECSA. Some LLVM IR estimations may not always be as accurate as at ISA level,

but they are still of value to developers. The LLVM optimizer and code emitter are the natural place for compiler optimizations. Transparency of energy consumption at this level enables programmers to investigate how optimizations affect their program's energy consumption, or even help introduce new low energy optimizations. This is more applicable at the LLVM IR level than at the ISA level, because more program information exists at that level, such as types and loop structures. The presented mapping techniques and analysis framework at the LLVM IR level are applicable to any compilers that use the LLVM common optimizer, provided that an energy model for the target architecture is available.

For some programs, indirect jumps that are introduced at the ISA level can make it impossible to extract a CFG. While this prevents ISA level ECSA, it can still be performed for these programs at LLVM IR, allowing programmers to gain energy consumption insight even where ISA level analysis is not feasible.

### 2.4 Related publications and dissemination

The mapping techniques for LLVM IR energy characterization have been used into two papers, for energy static analysis at the LLVM IR level. The first one, [GGP<sup>+</sup>15], was presented at SCOPES 2015 [Sco], and the second one, [LGK<sup>+</sup>15], is accepted to appear in *Foundational and Practical Aspects of Resource Analysis (FOPARA) 2015* [Fop]. A paper detailing the mapping techniques and their evaluation is attached as D2.3.3.

# 3 Multi-core modelling with communication costs

In a multi-core system of communicating software, both the core energy consumption and the communication energy consumption must be considered. Further, the timing impact of multi-core communication, and the increased latency in the movement of data, can have an impact upon execution time and therefore total system energy consumption.

Work during the D2.3 period has endeavoured to improve existing energy models and extend them to support these types of systems and software. An overview of this work is given here, and a paper detailing the research contributions and results from this work is attached as D2.3.1.

### 3.1 Improved core energy model

The work of [KE15a] is expanded upon in order to produce a more refined core energy model. This is achieved by performing additional profiling, capturing the energy consumption of a larger number of instructions. The remaining un-profiled instructions are modelled using a decision tree regression technique, where key instruction features are used to estimate energy, based on the demonstrated impact of those features when present in profiled instructions.

This work resulted in an improvement in average error to 2.67 % and also reduced the standard deviation of the results in the same set of benchmarks used on the original model. These model improvements can be fed into the higher level analysis that have been presented in deliverables D3.1 and D3.2, such as those published as [LKS<sup>+</sup>14] and [GGP<sup>+</sup>15].

## 3.2 VFS energy consumption modelling

Although not specific to multi-core or communication modelling, part of the modelling effort was put into voltage and frequency scaling (VFS), in response to the identification of savings that could be had when applying VFS in the examples given deliverable D5.1. Modelling that can be parametrised by operating voltage and frequency allows a broader range of design space exploration for the software developer.

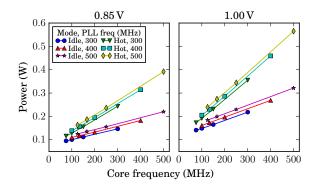

A VFS capable model was created by profiling a dual-core XMOS device with voltage scaling capabilities, the SLICEKIT-A16. This device contains two of the XS1-L cores modelled in [KE15a] and so provides a good base upon which to perform this further work. In addition to the processor cores, an analogue peripheral block sits on the processor network, one of the features of which is the control of the cores' 1 V supplies.

A set of profiling tests were constructed that exercised the SLICEKIT-A16 at idle and under load in various VFS states. The power data from this was then used to construct a characteristic

equation, parametrised by voltage, top-level system frequency and divided core frequency. The characteristic equations and their coefficients are given in the attachment D2.3.1.

The performance of the VFS modelling is good, with the model yielding a mean squared error against the profiling data of 2.6 % and total error range of 15.72 %. Given that the focus of research effort was put into multi-core and communication costs, further effort would be required in order to refine this version of the model and also demonstrate how it can be exploited. This is proposed as future work in D2.3.1.

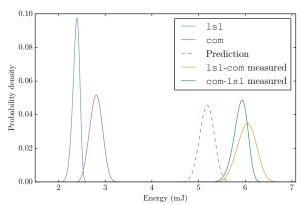

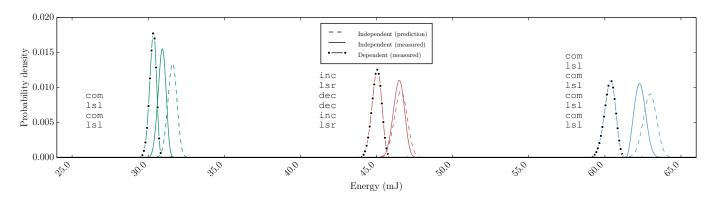

### 3.3 Multi-core energy consumption and communication

The multi-core energy modelling effort seeks to achieve two things:

- 1. Accurately estimate the overall energy consumption of a multi-core system when running communicating multi-core software.

- 2. Demonstrate effective methods for conveying *where* energy is consumed in the system, in order to guide the optimisation efforts of either tools or the developer.

Additional profiling was performed to establish the cost of communicating data tokens across the XMOS XS1's inter-node links. Simple models are then produced for the switch and interconnect based on the quantity of traffic that they carry.

A multi-core model is then created by assembling a graph representing the target XMOS system, reading data from the platform specification "XN" files used in the XMOS toolchain. Nodes in the graph are either cores or switches, and have the appropriate energy models attached to them. Edges represent links between these components, which again can have a model attached.

The modelling is enabled by trace data from the axe instruction set simulator. Several enhancements were made to axe, including:

- Accurately tracing *fetch no-op* FNOP activity in the core, to improve core model accuracy.

- Provide more accurate instruction traces, with finer-grained timing precision, to assist the core model's pipeline occupancy parametrisation.

- Issue traces for tokens traversing links, allowing them to be modelled.

- Implement the credit based flow control used within the XS1 switch network, providing more accurate multi-core communication timing and contention behaviours.

The latter point is particularly important as without it, no instruction set simulator for the XS1 architecture correctly simulates the time taken to communicate between cores. Our contributions use the link parameters given in the XN file to simulate the same communication speeds and latencies as realised in the hardware. This significantly improves timing accuracy of multi-core simulations, where previously the timing error would lead to very large, potentially unusable energy modelling errors.

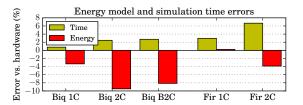

The timing model is demonstrated to have a sub-1 % error in the characterisation tests, and in larger benchmarks maintains single digit percentage error. This is two orders of magnitude better than what was previously available.

The simulator improvements are combined with the new graph-based network energy model and tested under the FIR and Biquad benchmarks presented in deliverable D5.1. The energy model error is shown to be less than  $\pm 10\%$ , with an average of -4.92% error.

In addition, a unique presentation method is shown, that highlights where the model has determined energy is being consumed. This is divided into cores, switches and links. This provides finer grained detail than normal hardware measurements provide, which typically give the overall system energy consumption, or a limited number of measurement points that capture multiple components simultaneously. This is used to demonstrate how a developer can identify the best way in which the software can utilise the hardware, considering optimal core utilisation as well as communication patterns. An explanation with examples, in the context of the Biquad filter benchmark, is given in attachment D2.3.1.

### 3.4 Dissemination

The work presented in this section is captured an attachment as D2.3.1 and is also available as a technical report [KE15b]. It will also shortly be submitted for peer-review with the intent to publish at an appropriate conference venue.

# 4 Worst case energy and defining data-aware energy models

Prior to concerns about energy consumption, execution time was an essential consideration for embedded systems software. Significant work has been presented that seeks to analyse programs to determine properties such as Worst-Case Execution Time (WCET) [WEE+08]. The ENTRA project's research into estimation of software energy consumption, can be framed in a similar way, whereby a worst case energy consumption is sought from the analysis of a program.

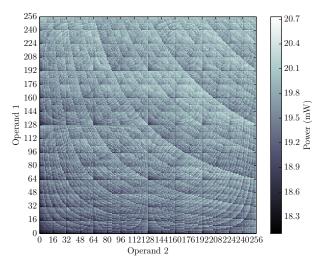

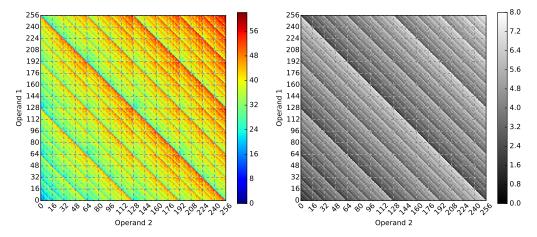

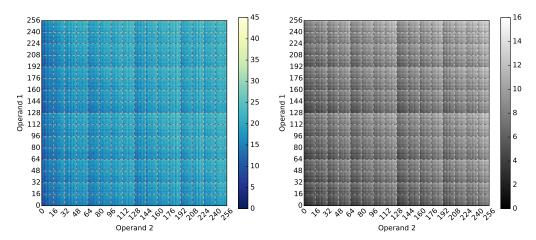

However, by the nature of energy consumption's relationship to power and time where  $E = P \cdot T$ , an extra dimension of complexity is introduced. This is because the power term, P, cannot be determined solely with respect to the instructions that a processor executes; the data that is used as input to, and produced as output from an instruction, has an effect on P even if T does not change.

Examination of prior work shows that data-dependant energy models for worst case or otherwise bounded energy consumption metrics have not been given any in-depth exploration. Thus, for more sophisticated, data dependant energy models to be applicable with confidence, further investigation was needed. In answer to this, in [PKME15] we present our methods and findings for the exploration of data dependant energy behaviour, as well as first steps towards modelling in this dimension. At the time of writing, this paper is currently being prepared for conference submission, and has been published in pre-print on arXiv. It is also included with this deliverable as attachment D2.3.2.

However, further research has revealed, that in the most general case, worst case analysis of data switching costs is infeasibly complex, both for a precise analysis and for any level of approximation. The optimization problem corresponding to calculating the worst case switching cost can be shown to be NP-hard, and in addition it can be shown that any approximation algorithm that guarantees a level of accuracy must also be NP-hard.

This theoretical result mandates a certain level of uncertainty in any worst-case energy estimation as the switching costs cannot be accurately estimated. Fundamentally, it must be asked whether worst case analysis can deliver a useful energy estimate given this limitation, and whether other avenues of exploration are worth following. Techniques such as the statistical analysis of data-dependent energy may become more significant given this uncertainty.

Our work on this topic is included with this deliverable as attachment D2.3.4, including background and analysis of the significance of data switching costs. It is currently under consideration for acceptance to a journal.

# 5 Energy modelling of application source code

A source-code level energy model is motivated by the gap that must be bridged in order to relate low level energy behaviour to the high level software. This work focuses on complex Java code forming a library for mobile gaming on Android devices. As such, this is substantially different to the pure C, embedded real time code examined in other parts of this and previous deliverables. However, the goals of the project still apply to this type of software development scenario and the techniques investigated in this section could be applied to other high-level languages.

This work establishes an energy model at the source code level, extracting energy costs for operations performed in the code from empirical measurement, which are then used to build a vector of energy costs for those operations. This model can then be applied to other applications that utilise the library to estimate their energy consumption characteristics.

This work reported in this deliverable is ongoing work.

### 5.1 Introduction and Motivation

The ENTRA project aims to support energy-aware software development, in contrast to the energy-oblivious manner typical today. Throughout the engineering life-cycle, developers are blind to the energy usage of the code written by themselves. On the other hand, it is estimated that energy saving by a factor of three to five could be achieved solely by software optimization [Edw11]. The approach of the ENTRA project is to achieve energy transparency through a combination of static analysis and energy modelling techniques, enabling the developer to understand the energy distribution among different parts of the source code.

In this section we focus on energy modelling. Traditional energy modelling methodology [TMW94, vBDMH00], including approaches adopted in the ENTRA project, is bottom-to-top. In this approach an energy model for machine level instructions is constructed, and this low-level model is mapped upwards to intermediate code and source code. This approach faces obstacles when the software stack consists of a number of abstract layers.

An alternative approach could be called top-to-bottom, and aims to construct a model directly for the source code, without any explicit low-level model. Intuitively, given a target device and power management strategy, the source code completely determines the energy consumption. The overall goal is to identify the basic energy-consuming operations from the source code and find the correlations to energy cost by analyzing a large amount of test cases. The resulting energy model implicitly includes the effect of all the layers of the software stack down to the hardware.

### 5.1.1 An experiment in source-code energy modelling

The target of the experiments described below is the Android platform. In February 2015, the penetration of smartphones was about 75% in the U.S. This figure is expected to reach 85% by December 2015 [Mar15]. With the improvement of hardware processing capability and software libraries for smartphones, applications are becoming heavier and more PC-like. At the same time, users are annoyed by limited battery capacity, as parallel-running applications could easily drain the full-charged battery within 24 hours. Thus energy-aware development for smartphones is becoming a critical requirement.

On the Android platform, say, the source code is in Java and translated to Java byte-code, further to Dalvik [Andb] (simplified Java virtual machine for Android) byte-code, native code and machine code and finally has chance to execute on the processors. Consequently, the modelling and mapping tasks in a bottom-to-top approach would have to address the complex problem of characterizing the links among all the layers. For this reason we attempt a top-to-bottom modelling approach for Android source code.

In the experiment, our target platform is an Android development board with two ARM quadcore CPUs, and the employed source code is a game engine which is for constructing games, demos and other interactive applications. The result shows that the inference model achieves an accuracy about 80%. Based on this model, we aim to capture the energy properties of the source code, such as energy hotspots, energy bugs and other opportunities for optimizing energy consumption.

## 5.2 Code to Energy

We build the energy model by analyzing a large set of execution cases. The brief procedure of mapping the source code to energy is 1) obtaining the precise execution path, 2) tracing the corresponding power consumption, 3) labelling test cases with the energy cost and 4) employing the labelled data to train the energy model.

Three factors play significant roles in building the inference model, which are execution-path obtaining, statement breakdown and model training. In the following sections, we will illustrate how to accurately acquire executed source code, why we need to breakdown statements and approaches in model construction.

#### 5.2.1 Block Division

We designed a large range of execution cases (in Section 5.3) to guarantee most corners in the source code are able to be covered. Not only the breadth of code coverage, the user interaction

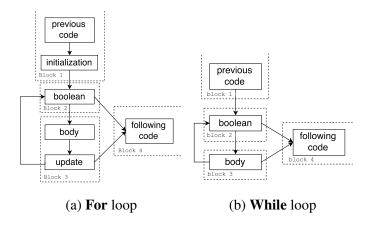

Figure 4: Block division of **for** and **while** loops in control flow graph

is also a significant dimension in the design space. As game applications are highly interactive, distinct input sequences result in huge varieties. The details of case design will be presented in Section 5.3.

**Definition 1** A block is a set of gathered statements. In the block, each node has only one inedge and one out-edge in the control flow graph, but the start point of the block could have more than one in-edge and the end point could have more than one out-edge.

A block is a fixed execution unit. That means, always if one part of the block is processed, the rest certainly will be executed. Its concept is declared in Definition 1. We choose the block as our basic sampling unit because tracing statements one by one has a vital impact on energy consuming and running time which damages the sampling precision. On the other hand, functions or classes are unstable execution unit, since we can not point out which certain parts the function or class will be active during run time.

For individual syntax structures, we deal with block division case by case. **For** loop an **while** loop are taken for examples as shown in Figure 4. In a **for** loop, the header usually has three segments which are *initialization*, *boolean* and *update*. According to Definition 1, the segments are divided into three different blocks. Following the same logic, we set the **while** header itself as a block.

The complete set of reached code points is acquired by recording the executions of blocks. We instrument the source code with a log instruction at the beginning of each blocks. It generates a block ID and a time stamp as one record in the log file which will be analyzed in later stage to obtain the execution path. As shown in Section 5.2.4, one execution case is corresponding to one input of the training model. The input features are extracted based on the path.

### **5.2.2** Basic Energy Operations

It is impossible to characterize the energy cost straightly based on individual statements because they varies largely, any pair of statements in the code are probably distinct. An arithmetic expression, say, could have two operators or three or more which could be additions or multiplications or mixed. In contrast, if we go to the function level, the model will be restricted to the domain of our target source code, since it's unlikely to find identical functions in different applications. We employ the "energy operation" as the basic modelling unit, such as arithmetic operations, comparison operations, method invocations etc. At the end, we in fact model the energy of individual operations. The entire energy consumption is made up of the cost of all operations in the code.

The operations (ops) are grouped into eight classes as shown in Table 2. In practice, these ops refer to one or more virtual machine instructions, but it is not important for the method to know exactly which ones. For example, the *multiplication* op with integer operands could be implemented by the *imul* instruction in the Java virtual machine instruction set [Ora] and then by other Dalvik opcodes [Andb]. The *block goto* op corresponds to the *jsr* instruction whose job is leading the CPU to an aimed subroutine. A basic assumption of our approach is that each of the source-level ops corresponds to a set of machine instruction which use a certain set of hardware components, which results in approximately the same energy cost each time it is called. This assumption may not always hold and other factors might also lead to different energy costs for different occurrences of the same op, leading to imprecision in the model, but it is an assumption that allows a reasonable estimate of energy consumption. Our experimental results show that the energy op is an appropriate intermediate representation to bridge the gap from source code to machine instructions, with regard to energy consumption.

#### 5.2.3 Data Collection

$$N_e(op_i) = \sum_{\substack{block_j \in BLK(op_i) \\ \{N_e(block_j) \cdot N_o(op_i, block_j)\} \\ where op_i \in Energy Ops}} \{N_e(block_j) \cdot N_o(op_i, block_j)\}$$

(1)

We developed a parser to extract the energy ops from the source code. All of the ops are labelled with the ID of the block where it resides. Note that, in the model building stage one record of training data couples one execution case, which is an one-on-one relation. One record consists of the numbers of executions of individual ops which are figured up according to Equation (1).  $BLK(op_i)$  is the set of blocks that contain  $op_i$ .  $N_o(op_i, block_j)$  means the occurrence of  $op_i$  in  $block_j$ .  $N_e(block_j)$  is the executions of  $block_j$ . Basically, the executions of  $op_i$  is equivalent to

the sum of the products of  $N_e(block_j)$  and  $N_o(op_i, block_j)$ .

Android applications utilize a rich range of Android's APIs and Java library classes where the fine-grained execution path is hard to capture. On the other hand, only a small proportion is frequently used during run time. We list the highly-referred library functions (Lib Funcs) in table 3, which are treated as special energy ops in the training stage. In particular, the GL10 class is the key interface for applications to implement their graphic computing.

### 5.2.4 Power Tracing & Model

In the experiment stage (Section 5.3), each execution case runs twice. In the first run, we record the execution path without power measuring. In the second time, we only trace power and disable the log instructions. We split the path and power obtaining work because the log instructions take up a part of the entire energy consumption which could not be neglected.

$$E = \sum_{i=1}^{n} power(t_i) \cdot \Delta_i, \quad (t_0 \le t_1 \le t_2 \dots \le t_{n-1} \le t_n)$$

(2)

The power trace is acquired by the measurement equipment, after which we approximate the energy cost (E) by calculating the integral of power, as shown in Equation 2. p = power(t) is the power-vs-time function, so  $power(t_i)$  is the measured power value at time stamp  $t_i$ . We let  $\Delta_i = t_i - t_{i-1}$  which is the interval between two sequential samplings.

$$E = \sum_{op_i \in Energy \, Ops} Cost_{op_i} \cdot N_e(op_i)$$

$$+ \sum_{func_i \in Lib \, Funcs} Cost_{func_i} \cdot N_e(func_i) + Idle \, Cost$$

(3)

The aimed model is formalized in Equation 3. The entire energy consumption consists of the sum of the costs of operations and library functions and idle cost. Notice that the idle costs of individual cases are different, since they are executed in distinct sequences of inputs, thus the lengths of sessions are also varying.

## **5.3** Experiment Setup

#### 5.3.1 Target & Power Measurement

Experiment target: Odroid-XU+E development board [Odr]. It possesses two ARM quad-core CPUs, Cortex-A15 with 2.0Ghz clock rate and Cortex-A7 with 1.5Ghz. The eight cores are

grouped into four pairs. Each pair consists of one big and one small core. So in the view of operation system, there are four logic cores. In our experiment, we turn off the small cores and only run workload on big cores at a fixed clock frequency of 1.1Ghz. This is for removing the influence of voltage, clock rate and CPU performance on power usage.

Power Measurement: Odroid-XU+E has a built-in power monitor tool to measure the voltage and current of CPUs with a sampling frequency of 30Hz and update the values in a file. We wrote a script to obtain the readings from the file every 0.1 second. During the test case, we run the script on a different core from where the application runs to minimize the interruption.

### 5.3.2 Source Code & Case Design

Our target source code is the Cocos2d-Android [Goo] game engine, a framework for building games, demos and other interactive applications. It also implements a fully-featured physics engine. The game is one of the main applications on smart devices, which has developed more and more PC-game-like, requiring a high CPU performance. The energy modelling and analysis research in this paper shows the opportunity to improve the source code and guide the software development towards energy efficiency.

We designed a large range of execution cases to simulate the game scenarios under different sequences of user inputs. We script with the Android Debug Bridge [Anda] (adb), a command line tool connecting target device to the host, to automatically feed the input sequences to the target board. For instance, in the Click & move scenario, the sprite (the character in the game) moves to the position where the tap is. We designed 10 input sequences with distinct tap positions and intervals. Each sequence is executed three times repeatedly. So for the Click & move, we have 30 execution cases.

### 5.4 Model Construction

The model construction is on the strength of machine learning, finding out the correlation between energy ops and costs from a large amount of data. We set out our collected data in the following matrices. The first one (N) from left is execution numbers of l ops (including energy ops and library funcs) in m test cases, which is observed by logging and calculating, as shown in Section 5.2. Each row indicates one test case. The vector  $(\overrightarrow{cost})$  in the middle contains the costs of l ops, which are the values we are aiming to obtain. The vector  $(\overrightarrow{e})$  on the right of equation mark is the energy cost computed by Equation 2. So for each test case, the energy cost is the sum of the costs of all the ops. It should be noticed that the energy cost has excluded the idle cost which is measured when no application workload is processing.

$$\begin{pmatrix}

n_1^{(1)} & n_2^{(1)} & \dots & n_l^{(1)} \\

n_1^{(2)} & n_2^{(2)} & \dots & n_l^{(2)} \\

& \dots & \dots & \\

n_1^{(m-1)} & n_2^{(m-1)} & \dots & n_l^{(m-1)} \\

n_1^{(m)} & n_2^{(m)} & \dots & n_l^{(m)}

\end{pmatrix} \times \begin{pmatrix}

cost_1 \\

cost_2 \\

\dots \\

cost_l

\end{pmatrix} = \begin{pmatrix}

e_1 \\

e_2 \\

\dots \\

e_{m-1} \\

e_m

\end{pmatrix}$$

(4)

Inevitably, the execution tracing and power measurement is not absolutely accurate. Meanwhile, the energy model is not exactly subject to the linear property. As a result, the equation above is unsolvable since the vector  $\vec{e}$  is out of the column space of N. To address this problem, we employ the well-known gradient descent algorithm [Ng12] to approximate the values of  $\vec{cost}$ .

The values of  $\vec{cost}$  are randomly set and then improved by the gradient descent algorithm step by step. We first introduce the error function J (Equation 5) which indicates the quality of the model.  $\vec{n^{(i)}}$  is the ith row in the first matrix,  $\vec{cost}$  is the middle vector above.  $\vec{n^{(i)}} \times \vec{cost}$  is the predicted energy cost for the ith test case,  $e^{(i)}$  is the observed energy cost. J is the sum of the squared errors of all the test cases, which is afterwards divided by 2m to get the average values. The reason why 2m is applied, but not m, is that 2m is convenient for the derivative computation later. So the smaller J is, the better  $\vec{cost}$  is.

$$J(cost_1, cost_2, ...cost_l) = \frac{1}{2m} \sum_{i=1}^{m} (\vec{n^{(i)}} \times \vec{cost} - e^{(i)})^2$$

(5)

The idea of gradient descent is to minimize J by repeatedly updating each element in  $\overrightarrow{cost}$  with Equation 6 until convergence. The partial derivative of J function on  $cost_j$  gives the direction in which increasing or decreasing  $cost_j$  will cut down J. The value  $\alpha$  determines how large the stride is in each iteration. If it is too large, the extremum value possibly will be missed; if too tiny, the minimizing process will be time-consuming. It needs to be manually tuned. Theoretically, the gradient descent algorithm could only find the local optimal value. In practice, the initial values in  $\overrightarrow{cost}$  are randomly set several times to look for the global optimization.

$$cost_{j} := cost_{j} - \alpha \frac{\partial J(cost_{1}, ...cost_{j}, ...cost_{l})}{\partial cost_{j}}$$

$$= cost_{j} - \alpha \frac{1}{m} \sum_{i=1}^{m} (\vec{n^{(i)}} \times \vec{cost}) \cdot \vec{n_{j}^{(i)}}$$

$$j = 1, 2, ...l$$

(6)

The algorithm above may produce  $\overrightarrow{cost}$  with negative elements, however as a matter of fact, the energy costs should be above zero. In view of this, we customize the original error functions

by adding a correction part for negative values, as shown in Equation 7. Smaller the negative cost is, larger the penalty is. The  $\lambda$  value balances the weight of correction part and that of the original part. The  $\rho$  value determines how aggressive the correction is. Both  $\lambda$  and  $\rho$  should be adjusted by hand. Consequently, the Equation 6 is re-written as Equation 8.

$$J = \frac{1}{2m} \sum_{i=1}^{m} (\vec{n}^{(i)} \times \vec{cost} - e^{(i)})^2 + \lambda \frac{1}{l} \sum_{j=1}^{l} \rho^{-cost_j}$$

(7)

$$\rho > 1$$

$$cost_{j} := cost_{j} - \alpha \frac{1}{m} \sum_{i=1}^{m} (\vec{n}^{(i)} \times \vec{cost}) \cdot \vec{n}_{j}^{(i)} + \alpha \lambda \frac{ln(\rho)}{l} \rho^{-cost_{j}}$$

$$j = 1, 2, \dots, l$$

(8)

### 5.5 Preliminary Results (Inference Accuracy)

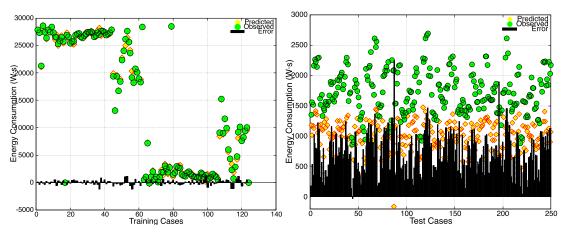

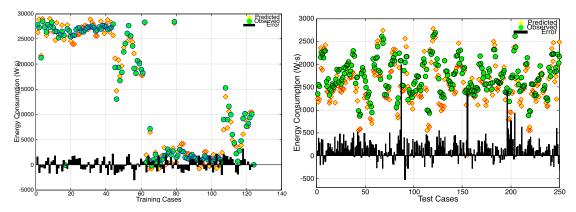

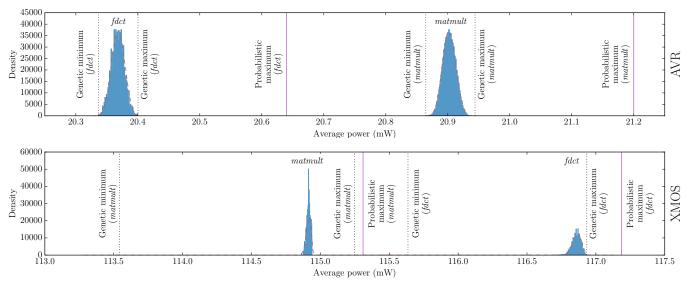

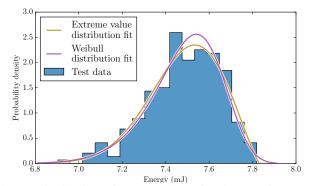

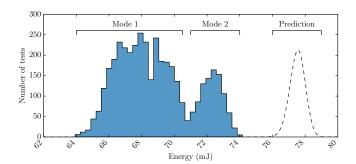

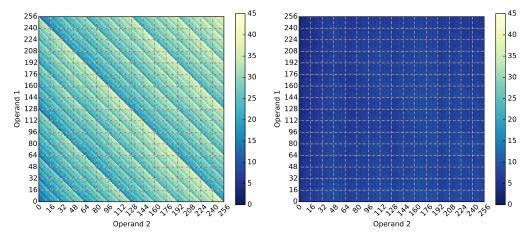

The key point of case design is to vary the executions of individual blocks, so we are able to enlarge the column space of the N matrix (in Section 5.4) to raise the possibilities to solve all the values in  $\overrightarrow{cost}$ . We try to achieve it by commenting out different sets of blocks in each test case. With the data collected in training cases, we obtain the approximate  $\overrightarrow{cost}$ . It is not trivial to note that the session lengths of test cases are about 5s, those of training cases are rather various from 5s to 40s, so as to broaden the view of the model. The inference accuracy of  $\overrightarrow{cost}$  in training and test cases is shown in Figure 5. The model fit the training cases quite well with an error margin of 2.2%. However, the error rate is unacceptably high in test, which is around 43.0%.

We find that the over-fit in train stage is because in most situations a set of energy ops are executed together, they are very hard to separate, for example, the comparison ops are always coupled with a block-goto op. To settle this, we apply an feature selection procedure. According to the training data, we put the op with strong linear execution correlations (above 0.9 and below 1.1) in the same group. The correlation is the covariance over the product of the standard deviations of two variables (op executions).

We then similarly treat one group of ops as one op to train the model. Figure 6 demonstrates that the inference error rate in training stage is higher than that before feature selection, about 7.2% and in test stage is much lower as 21.7%.

Figure 5: The predicted, observed energy consumption in training and test cases BEFORE feature selection. The bars show the errors of predicted values.

Figure 6: The predicted, observed energy consumption in training and test cases AFTER feature selection. The bars show the errors of predicted values

## 5.6 Dissemination

An article based on the work presented in this section has been submitted for peer-reviewed publication at a leading international conference venue.

| Benchmark    | Source Description      | Code structure & characteristics |      |   |          |          |          |   |    |          |   |

|--------------|-------------------------|----------------------------------|------|---|----------|----------|----------|---|----|----------|---|

| Benchinark   | Description Description |                                  | NCSL | T | L        | N        | A        | В | CP | MF       | C |

| Base64       | Online <sup>1</sup>     | Computes the base64 encoding     | 32   | 1 | ✓        |          | <b>√</b> | ✓ |    |          |   |

| Mac          | MDH                     | Dot product of two vectors       | 11   | 1 | <b>✓</b> |          | /        |   |    |          |   |

| Iviac        | WCET                    | and sum of squares               | 11   | 1 | >        |          |          |   |    |          |   |

| Levenshtein  | BEEBS                   | Measures the difference          | 26   | 1 | /        | /        | /        | / |    |          |   |

| Ecvensinein  | BEEDS                   | between two strings              | 20   | Ĺ | _        | Ľ        | Ľ        | Ľ |    | Ľ        |   |

|              |                         | Optimized Software Division      |      |   |          |          |          |   |    |          |   |

| Radix4Div    | Online <sup>2</sup>     | for platforms without            | 63   | 1 | ✓        |          | ĺ        | ✓ | ✓  |          |   |

|              |                         | hardware support                 |      |   |          |          |          |   |    |          |   |

|              | Online,                 | Software Division for            |      |   |          |          |          | 1 | ✓  |          |   |

| B. Radix4Div | modified                | platforms without hardware       | 37   | 1 | ✓        |          |          |   |    |          |   |

|              |                         | support                          |      |   |          |          |          |   |    |          |   |

| Cnt          | MDH                     | Counts non-negative numbers      | 29   | 1 | /        | 1        | <b>√</b> |   |    |          |   |

|              | WCET                    | in a matrix                      |      |   |          |          |          |   |    |          |   |

| Statistics   | MDH<br>WCET             | Statistics program               | 85   | 1 |          |          | ✓        | ✓ |    | ✓        |   |

| FIR          | XMOS                    | Finite Impulse Response          | 40   | 1 | ✓        |          | ✓        | ✓ |    |          |   |

| P. FIR_7T    | AMOS                    | filter                           | 103  | 7 | <b>✓</b> |          | ✓        | ✓ |    |          | ✓ |

| MatMul       |                         | Matrix multiplication of two     | 15   | 1 | <b>√</b> | <b>√</b> | <b>✓</b> |   |    |          |   |

| MatMul_2T    | MDH WCET                | square matrices                  | 25   | 2 | ✓        | ✓        | ✓        |   |    |          |   |

| MatMul_4T    |                         |                                  | 27   | 4 | ✓        | ✓        | ✓        |   |    |          |   |

| Biquad       |                         |                                  | 49   | 1 |          |          | ✓        | ✓ |    |          |   |

| Biquad_2T    | XMOS                    | Signal equaliser using           | 55   | 2 |          |          | <b>✓</b> | ✓ |    | <b>√</b> |   |

| Biquad_4T    | AMOS                    | biquad filtering                 | 57   | 4 |          |          | <b>√</b> | ✓ |    | ✓        |   |

| P. Biquad_7T |                         |                                  | 94   | 7 |          |          | <b>✓</b> | ✓ |    | ✓        | ✓ |

| Jpegdct      |                         | Performs a JPEG discrete         | 35   | 1 | <b>√</b> | 1        | <b>√</b> | ✓ |    |          |   |

| Jpegdct_2T   | MDH WCET                | WCET cosine transform            |      | 2 | <b>√</b> | ✓        | <b>√</b> | ✓ |    | <b>√</b> |   |

| Jpegdct_4T   | 1                       |                                  | 45   | 4 | <b>√</b> | ✓        | <b>√</b> | ✓ |    | <b>√</b> |   |

Table 1: Description and attributes of benchmarks.

$<sup>^1</sup>$  Retrieved from <code>http://stackoverflow.com/questions/342409</code>, Nov 2014.

$<sup>^2</sup>$  Retrieved from http://tinyurl.com/ld7exmd, Nov 2014.

Table 2: Energy Operations

| Addition, Subtraction    |  |  |  |

|--------------------------|--|--|--|

| Multiplication, Division |  |  |  |

| Increment, Decrement     |  |  |  |

| And, Or, Not             |  |  |  |

| Greater, Less, Equal     |  |  |  |

| Greater or equal         |  |  |  |

| Less or equal            |  |  |  |

| BitAnd, BitOr            |  |  |  |

| SignedBitShiftRight      |  |  |  |

| SignedBitShiftLeft       |  |  |  |

| Array reference          |  |  |  |

| Field reference          |  |  |  |

| Argument passing         |  |  |  |

| Returning value          |  |  |  |

| Block goto               |  |  |  |

| Function Invocation      |  |  |  |

| Declaration              |  |  |  |

| Type conversion          |  |  |  |

|                          |  |  |  |

Table 3: Library Functions

| Class       | Functions                                                     |  |  |  |  |

|-------------|---------------------------------------------------------------|--|--|--|--|

| ArrayList   | add, get, size, isEmpty, remove                               |  |  |  |  |

|             | glBindTexture, glDisableClientState                           |  |  |  |  |

|             | glDrawElements, glEnableClientState                           |  |  |  |  |

| GL10        | glMultMatrixf, glTexCoordPointer<br>glPopMatrix, glPushMatrix |  |  |  |  |

|             |                                                               |  |  |  |  |

|             | glTexParameterx, glVertexPointer                              |  |  |  |  |

| Math        | max, pow, sqrt, random                                        |  |  |  |  |

| FloatBuffer | position, put                                                 |  |  |  |  |

## References

- [ACM] Acm transactions on architecture and code optimization, at http://taco.acm.org/.

- [Anda] Android Android debug bridge. [Online: accessed 10.08.2015].

- [Andb] Android. Dalvik virtual machine. [Online: accessed 10.08.2015].

- [Edw11] Chris Edwards. Lack of software support marks the low power scorecard at DAC. In *Electronics Weekly*., pages 15–21, June 2011.

- [Fop] Foundational and practical aspects of resource analysis, at http://resourceanalysis.cs.ru.nl/fopara/.

- [GGP<sup>+</sup>15] Neville Grech, Kyriakos Georgiou, James Pallister, Steve Kerrison, Jeremy Morse, and Kerstin Eder. Static analysis of energy consumption for llvm ir programs. In *Proceedings of the 18th International Workshop on Software and Compilers for Embedded Systems*, SCOPES '15, New York, NY, USA, 2015. ACM.

- [Goo] Google. Cocos2d-android. [Online: accessed 10.08.2015].

- [KE15a] S. Kerrison and K. Eder. Energy Modeling of Software for a Hardware Multithreaded Embedded Microprocessor. *ACM Transactions on Embedded Computing Systems*, 14(3):1–25, April 2015.

- [KE15b] S. Kerrison and K. Eder. Modeling and visualizing networked multi-core embedded software energy consumption. *ArXiv e-prints*, September 2015.

- [LA04] C. Lattner and V.S. Adve. LLVM: A compilation framework for lifelong program analysis and transformation. In *Proc. of the 2004 International Symposium on Code Generation and Optimization (CGO)*, pages 75–88. IEEE Computer Society, March 2004.

- [LGK<sup>+</sup>15] U. Liqat, K. Georgiou, S. Kerrison, P. Lopez-Garcia, M. V. Hermenegildo, J. P. Gallagher, and K. Eder. Inferring Energy Consumption at Different Software Levels: ISA vs. LLVM IR. In *Proc. of the Foundational and Practical Aspects of Resource Analysis*, LNCS. Springer, 2015. To Appear.

- [LKS+14] U. Liqat, S. Kerrison, A. Serrano, K. Georgiou, P. Lopez-Garcia, N. Grech, M.V. Hermenegildo, and K. Eder. Energy Consumption Analysis of Programs based on XMOS ISA-level Models. In *Logic-Based Program Synthesis and Transformation*,

- 23rd International Symposium, LOPSTR 2013, Revised Selected Papers, volume 8901 of Lecture Notes in Computer Science, pages 72–90. Springer, 2014.

- [LLV14] LLVMorg. The LLVM Compiler Infrastructure, November 2014.

- [LM95] Yau-Tsun Steven Li and Sharad Malik. Performance analysis of embedded software using implicit path enumeration. In *Workshop on Languages, Compilers, & Tools for Real-Time Systems*, pages 88–98, 1995.

- [Mar15] Marketing Land. Report: U.S. smartphone penetration now at 75 percent, 2015. [Online: accessed 10.08.2015].

- [Ng12] Andrew Ng. CS229 lecture notes, 2012. [Online: accessed 10.08.2015].

- [Odr] Odroid. Odroid-XUE. [Online: accessed 10.08.2015].

- [Ora] Oracle. Java virtual machine instruction set. [Online: accessed 10.08.2015].

- [PKME15] James Pallister, Steve Kerrison, Jeremy Morse, and Kerstin Eder. Data dependent energy modelling: A worst case perspective. *arXiv preprint arXiv:1505.03374*, *Submitted to PATMOS 2015*, *under review*, 2015.

- [Sco] 18th International Workshop on Software and Compilers for Embedded Systems, at http://www.scopesconf.org/scopes-15/.

- [TMW94] V. Tiwari, S. Malik, and A. Wolfe. Power analysis of embedded software: a first step towards software power minimization. *Very Large Scale Integration (VLSI) Systems, IEEE Transactions on*, 2(4):437–445, Dec 1994.

- [vBDMH00] Tajana Šimunić, Luca Benini, Giovanni De Micheli, and Mat Hans. Source code optimization and profiling of energy consumption in embedded systems. In *Proceedings of the 13th International Symposium on System Synthesis*, ISSS '00, pages 193–198, Washington, DC, USA, 2000. IEEE Computer Society.

- [WEE+08] R. Wilhelm, J. Engblom, A. Ermedahl, N. Holsti, S. Thesing, D.B. Whalley, G. Bernat, C. Ferdinand, R. Heckmann, T. Mitra, F. Mueller, I. Puaut, P.P. Puschner, J. Staschulat, and P. Stenström. The worst-case execution-time problem Overview of methods and survey of tools. ACM Trans. Embedded Comput. Syst., 7(3), 2008.

- [XMO14] XMOS. xTimecomposer, November 2014.

# **Attachments**

The attachments referenced throughout this deliverable are included in this appendix.

# Attachment D2.3.1

Modelling software energy consumption in a multi-core network of embedded multi-threaded processors

In draft, awaiting submission.

## Modeling and visualizing networked multi-core embedded software energy consumption

Steve Kerrison and Kerstin Eder University of Bristol, United Kingdom firstname.lastname@bristol.ac.uk

Technical Report, August 2015

#### Abstract

In this report we present a network-level multi-core energy model and a software development process workflow that allows software developers to estimate the energy consumption of multi-core embedded programs. This work focuses on a high performance, cache-less and timing predictable embedded processor architecture, XS1. Prior modelling work is improved to increase accuracy, then extended to be parametric with respect to voltage and frequency scaling (VFS) and then integrated into a larger scale model of a network of interconnected cores. The modelling is supported by enhancements to an open source instruction set simulator to provide the first network timing aware simulations of the target architecture. Simulation based modelling techniques are combined with methods of results presentation to demonstrate how such work can be integrated into a software developer's workflow, enabling the developer to make informed, energy aware coding decisions. A set of single-multi-threaded and multi-core benchmarks are used to exercise and evaluate the models and provide use case examples for how results can be presented and interpreted. The models all yield accuracy within an average  $\pm 5\,\%$  error margin.

#### 1 Introduction

An increasing number of embedded systems now express their workloads through concurrent software. The parallelism present in modern devices, in forms such as multithreading and multiple cores, allow this concurrency to be exploited. This progression towards parallel systems has two main motivations. The first is in response to hitting operating frequency limits, where more work must now be done per clock in order to achieve performance gains in each new device generation. The other uses parallelism to allow work to be completed on time at a lower operating frequency, which can yield significant energy reductions.

However, parallel systems and concurrent software introduce complexities over traditional sequential variants that simply valued "straight-line speed". In particular, synchronisation of and exchanging information between concurrent components can negatively impact parallel performance if done inefficiently as per the well known *Amdahl's Law*. A good understanding of the software's behaviour, coupled with appropriate underlying hardware can overcome this if used correctly.

In embedded systems software, predictability is essential, both in terms of execution time, where real-time deadlines must be met, and in terms of energy consumption, where the supply of energy may be scarce. Time and energy are related through power, and while significant effort is put into timing predictable software, there remains both a lack of intuition and a lack of tools to help software developers determine the energy consumption of their modern embedded software components.

The research leading to these results has received funding from the European Union Seventh Framework Programme (FP7/2007-2013) under grant agreement no 318337, ENTRA - Whole-Systems Energy Transparency.

This report presents an energy model for a family of cache-less, time-deterministic, hardware multi-threaded embedded processors, the XMOS XS1-L series, which implements the XS1 architecture. These processors are programmed in a C-like language with message passing present in both the architecture and the programming model. The processors can be assembled into networks of interconnected cores, where the communication paradigm then extends across this network. The energy model must therefore be able to account for software energy consumption within each core as well as the timing and power effects of network traffic. To achieve this and also give developers better energy estimation tools, the following contributions are made:

- A multi-threaded energy model for the XS1-L [15] is extended to include more accurate instruction energy data, through greater instruction profiling and regression tree techniques.

- Support for Voltage and Frequency Scaling (VFS) is integrated into the model, the provide a richer environment for design space exploration by software developers.

- Several new features are added to axe, an Instruction Set Simulator (ISS) for the XS1-L, improving its core timing accuracy and introducing network timing behaviour, which has until now not been present in any simulators for these devices.

- The energy consumption of network communication is profiled, in order to extend the energy model to account for communication between multi-cores.

These contributions allow traces from the axe ISS to be analysed by the modelling framework, producing both text reports and visualisation of energy consumption across the network of processors in the system. The accuracy of this work is established through a series of multi-threaded, multi-core embedded software benchmarks. These are used to evaluate the effectiveness of the modelling and detail how it

can be used to aid a developer's design and implementation decisions.

Results show that the core model average error is 2.67% with a standard deviation of 4.40%, improving upon the prior work. The network capable model demonstrate an average error of -4.92%, with a standard deviation of 3.92%, supported by the VFS model with a mean squared error of 2.60% and total error range of 15.72%. The network model is shown to be suitable for determining the best approach for implementing two concurrent signal processing tasks on a target dual-core XS1-L platform.

#### Structure

The rest of this report is structured as follows. Related work is presented in Section 2, which looks at energy modelling of modern embedded processors, multi-core communication techniques and parallelism in embedded architectures, and summarises the particular implementations used in the XS1-L processor. The core- and network-level energy models are explained in Section 3, then the necessary ISS changes to support the model are presented in Section 4. Results from benchmarks exercising various parts of the model and simulation framework are discussed in Section 5 along with an evaluation of their performance in terms of accuracy and usability. Finally, Section 6 draws conclusions from this research and proposes future work.

#### 2 Related work and background

Energy modelling of software is motivated by a need to reduce global ICT energy consumption as well as to enable devices such as embedded systems to provide more features and last longer on limited source of energy. Although hardware actually consumes energy, it does so at the behest of software, which can be inefficient if the software does not fit well to the target hardware, or does not allow the hardware to exploit its own energy saving features [20].

Multi-core systems have proliferated through ICT, from servers in datacenters down to smart phones, and now even deeply embedded systems. Any endeavour to provide software energy consumption metrics must therefore be multi-core aware. In the rest of this section we discuss related work in three background areas. First is multi-core processors in embedded systems, next is energy modelling of processors, with a focus on software level energy consumption, and finally we introduce the XS1-L processor, the particular micro-architecture used as a case study for this research.

# 2.1 Parallelism and multi-core embedded processors

There are various ways of realising parallelism in processors. In embedded systems, many methods have been used VLIW (Very Long Instruction Word) has been used for some time, particularly in DSPs (Digital Signal Processors), where instruction packets enable software pipelining to be parallelised. Multi-core is becoming more prevalent, where it is beneficial to replicate a core several times and distribute work between cores. This has become necessary to provide performance gains as frequency increases have become harder to realise within practical power budgets [13].

High performance embedded processors, such as those found in smart phones, can feature multiple cores with different micro-architectures. ARM's big.LITTLE is the seminal example of this, where programs can be scheduled onto simpler cores when low-energy operation is necessary or appropriate. The little cores are slower, but can be operated at a lower voltage and frequency point than their big counterparts, consuming significantly less energy. In big.LITTLE, significant effort is put into cache coherency between the cores, and migrating tasks can require flushing and copying of core-local caches in order to keep consistent state.

Smaller processors, such as ARM's Cortex-M series, can also be used in multi-core, but the implementation is defined by the manufacturer. ARM has made recommendations on how to construct such devices, including cache and memory arbitration mechanisms [27]. Older generation ARM9 processors have been assembled in their thousands in the *SpiNNaker* system [5].

Rather than connecting processors via a cache hierarchy and memory bus, some systems implement a network of cores. Devices such as the Adapteva Epiphany [1] and EZChip TILE [4] processors feature many cores in a Network-on-Chip, with a grid topology of interconnects between them. In both of these processors there are multiple networks, each serving a unique purpose, such as I/O, cache coherency and direct inter-tile communication. The Intel Xeon Phi [12] uses a ring network and a hierarchy of processors, caches, tag directories and memory controllers to create a NoC that can also be viewed as a traditional memory hierarchy. Its use is not in embedded systems, but rather as a high performance computing accelerator.

The XS1-L processor features no cache hierarchy and can be assembled into a network of cores where channel style communication is possible both on- or off-chip. This is discussed in more detail in Section 2.3.

#### 2.2 Energy modelling of processors

A program's energy consumption is the integral of a device's power dissipation during the course of execution:

$$E = \int_{t=0}^{T} P(t) dt, \qquad (1)$$

although this is frequently represented using an average power, giving  $E=P\times T$ . To energy model a processor, P must be estimated over the course of T with sufficient granularity and precision to provide a desired accuracy. At the hardware level, detailed transistor or CMOS device models can be used, and every change in circuit state simulated to determine a fine-grained power estimation. This is time consuming and requires access to the RTL description of a processor, making this form of analysis infeasible for software developers.

Higher level models can be used instead, such as those modelling the processor as functional blocks. Instructions issued by the processor trigger activity in the functional blocks, and a cost is associated with that, which can be used to estimate the energy consumption of a sequence of instructions. At this level, the instructions are an essential part, as these drive the modelling, but also form a connection to the software — the instruction sequences for a given architecture are related to the software developer's

program via transformation by a compiler. The ISA therefore provides a good level at which to perform analysis of hardware energy consumption at the behest of software.

Seminal work in ISA level energy modelling includes that of Tiwari et al. [26], where sequences of instructions are assigned costs, as well as the transitions between instructions, which causes circuit switching as new control paths are enabled. This work has been drawn up upon to enable energy consumption simulation frameworks such as Wattch [3] and SimPanalyzer [24]. This style of ISA level modelling has also been refined to include finer grained detail on the activity along the processor data path, where data value changes also influence energy consumption [25].

Energy modelling has been performed for a wide variety of processors with various micro-architectural characteristics, for example VLIW DSP devices [10], both simple and high performance ARM variants, as well as very large processors such modern server grade x86 devices [8] and the 61 core Xeon Phi [23]. These all draw from similar background, but account for different processor features, and obtain their model data from different sources. For example, high performance ARM and x86 models can use hardware performance counters to model activities such as cache misses, which have a significant impact on energy consumption. Simpler devices may not be so affected, and thus direct instruction level costs can be attributed. Parametrised energy models that consider properties such as operating frequency and voltage have been created for other processors, such as the Intel Xeon in [2], to inform a model predictive controller in order to smooth thermal hotspots in such dense multi core devices.

A single core model of the XMOS XS1-L architecture is presented in [15], which uses data from a series of instruction energy profiling tests in order to build the model. The architecture's hardware multi-threading is accounted for, with the level of parallelism (active threads) contributing to energy consumption during the course of the analysed program. This model has been applied using instruction set simulation, and also via static analysis at the ISA level [7, 16] as well as the LLVM IR level [6].

#### 2.3 The XS1-L processor and network

The XS1-L family is a group of processors implementing the XMOS XS1 ISA in a 65 nm process technology, featuring a configurable network upon which arbitrary topologies of interconnected processors can be built. Each core has a four stage pipeline and support for up to eight hardware scheduled threads. A thread can have no more than one instruction in the pipeline at any given time, therefore the XS1-L parallelism is only fully utilised if four or more threads are active.

These processors include 64 KiB of single cycle SRAM and have no cache, therefore the memory subsystem is flat and requires no special considerations with respect to timing. The majority of instructions complete in four clock cycles, with the exception of the divide and remainder instructions and any instructions that block on some form of I/O. If more than four threads are active, then the instruction issue rate per thread will reduce proportionally, but the instruction throughput of the processor remains the same. This makes timing analysis of the processor very

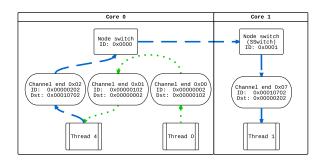

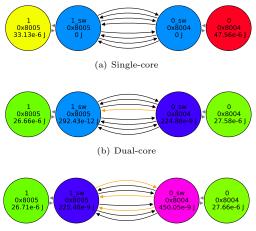

Figure 1: Visualisation of channel based communication between threads both locally and between cores.

predictable, allowing tight bounds or even exact values to be produced.

The XS1 instruction set includes provisions for resource operations. These are interactions with peripheral devices, such as I/O ports, synchronisers and communication channel endpoints (chanends). As such, activities such as I/O are a first class member of the instruction set. Other instruction sets, such as x86, have similar provisions [11, pp.115,176]. However, the XS1 architecture takes this further, and places these peripherals outside of the memory space, such that I/O and other resource operations are not translated into memory mapped reads and writes, but are instead a completely separate data path. This separation of memory and resources aids in the modelling processor, particularly when communication between threads and cores is considered.

On a single core, it is possible for threads to communicate or access common data using shared memory paradigms. This can be expressed in software through appropriate use of regular pointers in C, or through specially attributed pointers in version 2 of the XC language that was developed to complement XS1. However, CSP style channel communication is more prevalent in XC. Channels in XC translate into channel endpoints in the XS1 architecture, where two chanends are logically connected together. Communication then takes the form of in and out instructions. Control tokens can be used to provide synchronisation, and instructions will block if buffers are full or no data is available to read. This paradigm extends beyond core-local communication and out onto a network of cores. Therefore, concurrent programs can grow to use multiple processors with relative ease.

A network of XS1-L processors consists of multiple cores each connected to their own integrated switch. This switch provides a number of links, which can be connected to other switches, either on- or off-chip. These links can operate in either five- or two-wire mode in each direction, where the former can carry two bits per symbol and the latter one bit per symbol in an 8b/10b encoding. The five wire mode is therefore faster at the same frequency, but requires ten wires total per link. Each link possesses a receive buffer and credit based flow control is used to prevent overrun. When a link is first enabled, the sending switch must solicit credit from the switch at the other end of the link with a hello token. During normal operation, credit tokens are

sent from the receiver to the sender as buffer space becomes available.

Routing between switches is configurable based on IDs assigned to each node, where a node is a switch and its associated core. When a message is first sent from the chanend of a core, the ID of the destination node is prepended to the message. Receiving switches then compare this ID to their own. If they are different, the first bit that is different is used to determine the direction along which the message will be routed. A direction can be assigned one or more links, and the next available link in that direction will then be used for forwarding. Typically, dimension-order routing is used to create a deadlock avoiding network, but this is dependent upon the topology network that is physically assembled. Links are held exclusively by the source chanend either indefinitely, or until a closing control token is transmitted from the source. Through this approach, both wormhole routed packets and permanently reserved streaming routes can be created.

A high level view of threads communicating through chanends and switches, both locally and between cores is shown in Figure 1. The precise implementation details and configuration parameters are detailed in [18, 19]. Examples of multi-core XS1 implementations include the XMP-64, which features 64 cores, using the older XS1-G family, and the Swallow project, which assembles multiple dual-core XS1-L family processors into a system of hundreds of cores [9]. These use hypercube and lattice network topologies, respectively.

#### 3 XS1-L core and network energy model

In this report, the modelling effort of [15] is extended in several ways. Firstly, more instructions are directly energy profiled, and for those that cannot, a regression tree approach is implemented to estimate their energy cost. Secondly, additional voltage and frequency profiling is performed, using a suitable variant of the XS1-L, to produce a VFS aware model version, retaining good error bounds. Finally, network communication costs are considered, through further profiling, and a network level, communication ware model produced, integrating core, switch and interconnect components within the model.

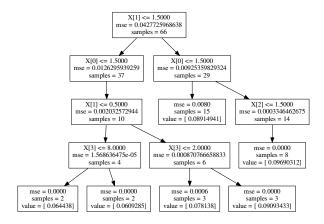

#### 3.1 Regression tree

The prior work of [15] investigated grouping instructions by operand count in order to provide an energy estimate for un-profiled instructions, as well as to reduce model complexity. However, the evaluation showed that this was not suitably fined grained or sufficiently accurate. Instead, each profiled instruction is accounted for individually, and un-profiled instructions are assigned a default value, based on the observed average of all profiled instructions.

Here, a different approach is used, where a set of instruction features are used to classify each instruction. This is combined with the direct instruction profiling data into a regression tree, allowing un-profiled instructions to receive an energy estimate based on profiled instructions with similar features.

Figure 2: Visualisation of part of the model regression tree. Leaves provide energy estimations, all other nodes are decisions based on a particular instruction feature X[f]. Not all branches are shown; the full tree is 29 nodes.

|           | Features |   |   |    |   |   |                  |

|-----------|----------|---|---|----|---|---|------------------|