# **ENTRA**

318337

**Whole-Systems ENergy TRAnsparency**

# **Energy Optimization: Advanced Techniques (including SW demo)**

Deliverable number: D4.2

Work package: Optimization (WP4)

Delivery date: 1 October 2015 (36 months)

Actual date: 1 March 2016 Nature: Prototype

Dissemination level: PU

Lead beneficiary: Roskilde University

Partners contributed: Roskilde University, University of Bristol, IMDEA Software Insti-

tute, XMOS Limited

Project funded by the European Union under the Seventh Framework Programme, FP7-ICT-2011-8 FET Proactive call.

## **Short description:**

This deliverable presents results relating to tools and methods supporting energy optimisation. Both static and dynamic techniques are covered.

The deliverable includes the following attachments:

- D4.2.1: Stochastic vs. Deterministic Evolutionary Algorithm-based Allocation and Scheduling for XMOS Chips. Neurocomputing, Vol. 150, pages 82–89, Elsevier, February 2015.

- D4.2.2: Energy Efficient Allocation and Scheduling for DVFS-enabled Multicore Environments using a Multiobjective Evolutionary Algorithm. Genetic and Evolutionary Computation Conference (GECCO 2015), pages 1353–1354, ACM, 2015.

- D4.2.3: Trading-off Accuracy vs. Energy in Multicore Processors via Evolutionary Algorithms Combining Loop Perforation and Static Analysis-based Scheduling. Hybrid Artificial Intelligent Systems (HAIS 2015), Lecture Notes in Computer Science, Vol. 9121, pages 690–701, Springer International Publishing, 2015.

- D4.2.4: *Improved Energy-aware Stochastic Scheduling based on Evolutionary Algorithms via Copula-based Modeling of Task Dependences*. International Conference on Soft Computing Models in Industrial and Environmental Applications (SOCO 2015), Advances in Intelligent Systems and Computing, Vol. 368, pages 153–163, Springer International Publishing, 2015.

- D4.2.5: A Practical Approach for Energy Efficient Scheduling in Multicore Environments by combining Evolutionary and YDS Algorithms with Faster Energy Estimation. The 11th International Conference on Artificial Intelligence Applications and Innovations (AIAI'15), IFIP Advances in Information and Communication Technology, Vol. 458, pages 478–493, Springer, 2015.

- D4.2.6: *Genetic Algorithm-based Allocation and Scheduling for Voltage and Frequency Scalable XMOS Chips*. Hybrid Artificial Intelligent Systems (HAIS 2013), Lecture Notes in Computer Science, Vol. 8073, pages 401–410, Springer, 2013.

- D4.2.7: An Energy-Aware Programming Approach for Mobile Application Development Guided by a Fine-Grained Energy Model. Technical report, Roskilde University, February 2016. to be submitted for publication.

# Contents

| 1  | Intr  | oduction                                                                      | 3  |

|----|-------|-------------------------------------------------------------------------------|----|

| 2  | Glol  | oal optimiser                                                                 | 3  |

|    | 2.1   | Introduction                                                                  | 4  |

|    | 2.2   | Rationale                                                                     | 5  |

|    | 2.3   | Invocation from tools                                                         | 7  |

| 3  | Dua   | l-issue processing                                                            | 9  |

|    | 3.1   | Introduction                                                                  | 9  |

|    | 3.2   | Dual issue design                                                             | ç  |

|    | 3.3   | Extra instructions to support dual issue                                      | 10 |

|    | 3.4   | Example dual issue                                                            | 11 |

| 4  | Ene   | rgy-accounting for Android app energy optimisation                            | 12 |

|    | 4.1   | Case study outline                                                            | 13 |

|    |       | 4.1.1 Basic Energy Operations                                                 | 14 |

|    |       | 4.1.2 Energy Model                                                            | 15 |

|    | 4.2   | The Click & Move Scenario                                                     | 15 |

|    |       | 4.2.1 Code optimisation                                                       | 18 |

|    |       | 4.2.2 Evaluation                                                              | 23 |

|    | 4.3   | The Orbit Scenario                                                            | 23 |

|    |       | 4.3.1 Energy Accounting                                                       | 23 |

|    |       | 4.3.2 Code optimisation                                                       | 24 |

|    |       | 4.3.3 Evaluation                                                              | 25 |

|    | 4.4   | The Waves Scenario                                                            | 26 |

|    |       | 4.4.1 Energy Accounting                                                       | 27 |

|    |       | 4.4.2 Code optimisation                                                       | 28 |

|    |       | 4.4.3 Evaluation                                                              | 28 |

|    | 4.5   | Conclusion                                                                    | 29 |

| 5  | Dyn   | amic optimisations: energy-aware scheduling in multicore environments         | 30 |

| Α1 | tachn | nents                                                                         | 33 |

|    | D4.2  | 2.1: Stochastic vs. Deterministic Evolutionary Algorithm-based Allocation and |    |

|    |       | Scheduling for XMOS Chips                                                     | 35 |

| D4.2.2: Energy Efficient Allocation and Scheduling for DVFS-enabled Multicore En-   |    |

|-------------------------------------------------------------------------------------|----|

| vironments using a Multiobjective Evolutionary Algorithm                            | 44 |

| D4.2.3: Trading-off Accuracy vs. Energy in Multicore Processors via Evolutionary    |    |

| Algorithms Combining Loop Perforation and Static Analysis-based Scheduling . 4      | 47 |

| D4.2.4: Tree Automata-Based Refinement with Application to Horn Clause Verification | 60 |

| D4.2.5: A Practical Approach for Energy Efficient Scheduling in Multicore Environ-  |    |

| ments by combining Evolutionary and YDS Algorithms with Faster Energy Es-           |    |

| timation                                                                            | 71 |

| D4.2.6: Genetic Algorithm-based Allocation and Scheduling for Voltage and Fre-      |    |

| quency Scalable XMOS Chips                                                          | 88 |

| D4.2.7: An Energy-Aware Programming Approach for Mobile Application Develop-        |    |

| ment Guided by a Fine-Grained Energy Model                                          | 99 |

# 1 Introduction

This deliverable presents results relating to tools and methods supporting energy optimisation. There are four main sections to the report. The global optimiser and the dual-issue processor constitute the main "prototype" contained in the deliverable.

- In Section 2 we describe the global optimiser included as of Release 14 of the XMOS tools; this is a stage in the XC build process where whole-program analysis is performed in order to improve energy behaviour.

- In Section 3 we give an overview of the XMOS XS2 architecture supporting dual-issue, that is, the ability to execute two instructions simultaneously during one clock cycle. A key motivation for this architecture is that it cuts the energy overhead associated with executing instructions, involving distributing clocks, maintaining program counters, resources, etc.

- In Section 4 we describe a case study in static energy optimisation of source code based on energy transparency. The case study deals with Android app code, for which detailed energy accounting is performed based on a source code energy model. This leads to manual optimisations of the most energy-consuming parts of the code, which save up to 50% of energy in some use scenarios. This work is being further developed and being incorporated into tools supporting energy-aware mobile app development.

- In Section 5 we present a summary of a body of theoretical and experimental work on *dynamic* energy optimisation. Dynamic energy optimisations aim to use an energy model to make intelligent run-time decisions on task allocation in multicore multithreaded environments with the possibility of voltage and frequency scaling, with given constraints and requirements on performance. This work relies heavily on ENTRA tools for energy modelling and analysis to provide the information needed for the optimisation algorithms.

# 2 Global optimiser

As of release 14, the XMOS tools incorporate a global optimiser; a stage in the build process where whole-program analysis is performed in order to improve energy behaviour.

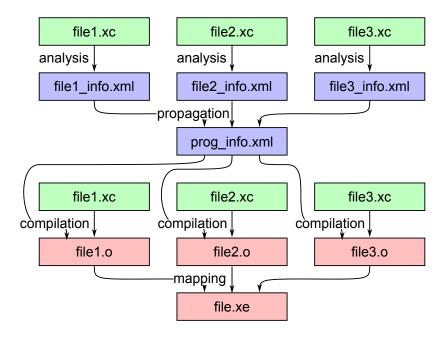

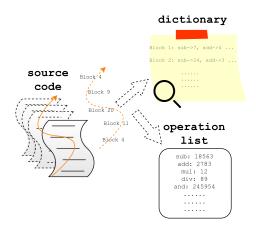

Figure 1: Global optimiser structure

#### 2.1 Introduction

The global optimiser is a stage in the build process that analyses the call graph of an XCORE program, and performs global constant propagation throughout the program, enabling later stages in the compiler to generate efficient code.

The reason why a special phase was invented rather than taking a more traditional approach is that:

- We need intra-modular analysis, going across boundaries of source files

- We need source-level analysis, because once we have reached the LLVM intermediary level we have lost too much semantic information

This leads us to a tool that works as shown in Figure 1. It comprises three stages:

• A tool to analyse a single source file, and to write the results of that analysis into an XML file that identifies function definitions, function calls, and constants. This tool is built into the front end, and a flag on the front-end emits the XML file instead of performing a compilation.

- A tool that takes all the XML source files, and based on this provide specialisations for (each of) the source functions. This is a new tool, xpca, it generates a single XML file that contains all the information.

- Based on the output of xpca, modules are recompiled. The final compilation stage uses the program information file to specialise specific functions.

#### 2.2 Rationale

There are two reasons to implement a global optimiser.

- The first reason is that it can improve the energy profile of existing code

- The second reason is that it enables software engineers to design their software in a more modern, concise and consistent way.

The latter point is especially relevant; it is very easy to write energy efficient software on a small scale. It is hard to properly engineer efficient software in such a way that it can be reused, maintained, and read without specialist knowledge.

Interfaces (see Deliverable D1.2) were introduced to aid in software engineering; but their generic implementation is not efficient. It is the combination of interfaces and the global optimiser which creates a potent tool that generates code that is more efficient than naively written code.

Depending on how the interface is used, the global optimiser may recover some or all inefficiencies caused by the interface itself. As an example, consider the I2C interface illustrated in D1.2:

```

int send_stop_bit) -> i2c_res_t result:

...

locked_client = send_stop_bit ? -1 : i;

result = (ack == 0) ? I2C_ACK : I2C_NACK;

break;

case c[int i].send_stop_bit(void):

...

locked_client = -1;

break;

...

}

```

This interface works on n clients, where n is chosen by the application designer. A common choice is 1 client only, in which case the code below will optimise to remove all the case-sequences, remove the guards, remove the locked\_client variable, and all array bound checks on the c array.

Further optimisations happen because not all parts of the interface may be used. Say that the client only uses the read() call, but never writes data, and it always sends the implicit stop bit, never calling the send\_stop\_bit() call. In that case, the code for these will be removed. This will not improve energy efficiency, but it will reduce the memory footprint of the application, which agains supports software engineering and avoids designers having to make bespoke versions of interfaces.

An evaluation of the global optimiser is part of Deliverable D6.2.

Aside from optimising the interfaces, the global optimiser enables software modules to be configured in a way that does not require a pre-processor. If we take a UART as an example, then there is two ways to configure the UART. Configuration using #define lines requires those to be included in the right files through a user defined include-file that is included by the module; uart\_conf.h would contain:

```

#define UART_PARITY 0 // Disable parity

#define UART_STOP_BITS 1 // One stop bit

#define UART_BAUD_RATE 9600 // Speed to run at

```

And then there would be some magic that causes all UART source files to include this configuration header file. Alternatively, the UART module would allow configuration through the instantiation of the thread. The uart.h include file contains the definition of the uart thread:

```

extern uart_thread(in parity, int stop_bits, int baud_rate);

```

And the main program invokes the thread with the appropriate parameters:

```

#incude <uart.h>

main() {

par {

uart_thread(0, 1, 9600);

}

}

```

With the global optimiser, these two options are now identical in terms of energy usage and speed; however, the latter option is preferable from a software perspective as there is no magic involved in importing the defines into the library

#### 2.3 Invocation from tools

The XMOS tool chain will automatically invoke all the tools necessary. Since the XMOS tool chain contains the full build system (including the dependency checker), it has full control anyway, and it is straightforward to call the analysers and global optimisers in a transparent manner. This is shown in Figure 2.

```

[14:46:18 % xmake

Checking build modules

No build modules used.

Analyzing fir.xc

Analyzing main.xc

Analyzing voltage.xc

Propagating analysis

Creating dependencies for voltage.xc

Creating dependencies for main.xc

Creating dependencies for fir.xc

Compiling fir.xc

Compiling main.xc

Compiling voltage.xc

Creating app_seqproject.xe

Build Complete

14:46:26 %

```

Figure 2: XMAKE screenshot

One can see that the build process comprsies five steps, three of which (steps 1, 2, and 4) relate to the global optimiser. Step one analyses all the source files that have been changed since the last build. Step two propagates the analysis, incorporating the analyses of source files that have not been changed. Step three creates dependencies. Step four performs the modular compilation, using the propagated global optimisation analysis. Step five builds the final object.

Users of the XMOS tools release 14 (and beyond) are using globally optimised code by default.

# 3 Dual-issue processing

#### 3.1 Introduction

Of the total energy consumed by a device when executing a program, a large fraction of this time is related to overhead involved in executing a program; that may involve distributing clocks, maintaining program counters, resources, etc.

Given this observation, we have developed the XS2 architecture that supports dual issue: executing two instructions simultaneously during one clock cycle.

Executing dual issue, means that we can execute the same code in fewer clock cycles, consuming less power due to a cut in the overhead.

# 3.2 Dual issue design

The dual issue design of the XS2 architecture pivots around the two *lanes* that are used to execute instructions. The lanes are not symmetrical, for that would have added an unreasonable amount of logic and complication. Instead, the lanes are specialised as follows:

**IO** Lane The IO Lane can be used to execute all resource instructions, instructions that modify the thread state (such as the status register), and all basic arithmetic operations.

**Memory lane** The Memory Lane can be used to execute all memory operations (load, store, and branch operations, including subroutine call and return), and all basic arithmetic operations.

Hence, resource instructions can only execute in the left pipeline, and memory instructions can only execute in the right pipeline:

- It is not possible to dual issue two resource operations. Allowing this would have complicated the resource logic to deal with multiple simultaneous operations and would have added to the energy profile of the processor.

- It is not possible to dual issue two memory operations. Allowing that would have forced another port on the memory.

- It is possible to dual issue two basic operations (eg, add and add).

- It is possible to dual issue basic operations with either IO, or memory.

- It is possible to dual issue a memory operation with a resource operation.

• Two operations should never write to the same register.

Many of the inner loop that XCORE programs exhibit show a mixture of memory and resource operations, or memory and arithmetic operations. For example, a loop to input or output a block of data uses a resource operation and a load/store operation. They depend on each other, but by unrolling the loop once they can be dual issued. Similarly, memory and arithmetic are a normal combination.

In addition to the simple arithmetic operations there are complex operations such as multiply, divide, long add, CRC, etc. All of these instructions are rarer, may be associated with a large number of gates, and may have many input and output operands. They are encoded in a long 32-bit encoding, and are executed in single issue. All dual issuable instructions are encoded in 16-bits and can be executed side by side.

# 3.3 Extra instructions to support dual issue

A number of instructions have been added to the instruction set to further improve energy performance, and to partly counteract the restrictions above:

- Dual load and store instructions have been added. They are long instructions that fetch (store) a pair of words from an address that is double word aligned. A full dual issue machine would enable an arbitrary pair of words to be loaded; being able to load a pair of subsequent words is a useful intermediary for many uses. For example, complex numbers, coefficients of filters, subsequent items in a queue, or subsequent items in a datablock can all be load/stored at twice the speed using these instructions.

- Similarly, dual load and store instructions for the stack have been added that facilitate more efficient function entry and exit blocks.

- A few extra arithmetic instructions have been added to encode sequences of dependent instructions. In particular, saturating arithmetic, extracting the result, and extracting/inserting words of data are supported. They are difficult to perform efficiently in dual issue code as there are data dependencies that make dual issue hard.

- A DUALENTSP instruction is added that marks the entrance to a piece of dual issue code. This way, each function can be written in either dual or single issue; and code that has to be energy efficient can be made to run in dual issue, whilst code that has to be memory efficient can be written in single issue.

Finally, a dedicated NOP instruction has been added. Dual issue slots that cannot be used must be filled by a NOP instruction. Traditionally, the XS1 architecture supported a large number of instructions that are effectively NOP instructions, such or r0, r0, r0, or r1, r1, r1, add r11, r11, 0. However, all these instructions always write into a register, and it would be problematic if the other lane wrote in the same register. It also uses less power.

# 3.4 Example dual issue

As an example of how dual issue with the other instructions work out, we show the inner loop of an FFT on XS2 below:

```

innerLoop1:

ldd r3, r6, r4[0]

ashr r6, r6, 1

ashr r3, r3, 1

ldd r2, r5, r4[r9]

ldd r10, r7, sp[10]

maccs r8, r7, r5, r1

maccs r8, r7, r2, r0

{ldc r7, 0

; neg r5, r5 }

maccs r7, r10, r5, r0

maccs r7, r10, r2, r1

{add r6, r6, r8 ; sub r8, r6, r8 } // Cross use

{add r3, r3, r7; sub r7, r3, r7} // Cross use

std r3, r6, r4[0]

std r7, r8, r4[r9]

{ldw r6, sp[16] ; sub r4, r4, r11 }

{lsu r8, r4, r6 ; nop

r8, innerLoop1 ; nop

{bf

```

- This loop comprises 17 issue slots; executing 21 instructions. Superficially, this is a disappointing issue rate of 1.23 instructions/thread cycle. However, the loop also contains five double loads and stores, that are actually shortcuts for dual-issued loads and stores. Hence, a fair metric is that it executes 26 instructions in 17 issue slots, giving an issue rate of 1.52 instructions/thread cycle. This reduces power by a third.

- The code has an interesting feature in issue slots 11 and 12 (marked Cross use). In these slots, the destination operands in both lanes, are also source operands in both lanes.

Each instruction uses R6 and R8, and the left lane writes into R6 whereas the right lane writes into R8. This piece of code cannot be serialised into single issue, for it would either overwrite R6 or R8 before the register is dead. Indeed, executing this code in single issue requires a register to be spilled, which would add a total of four instructions to the loop. This brings the comparable single issue code to take 30 thread cycles; compared to 17 thread cycles for the dual issue code, a reduction of a factor of 1.75.

• The final difference stems from the new pre-fetch mechanism. To keep the dual issue pipeline going the instruction buffers had to be extended, and more data is kept in them. Due to this, the total number of thread cycles saved compared to the old single-issue architecture is close to a factor of 2.

The improvement in issue rate of nearly a factor of 2 is offset by slightly higher power consumption due to the extra lane. It is very difficult to perform a precise comparison because various other parts of the processor were improved (for energy efficiency), however, we think that overall on average we save between a factor of 1.5 and 2.

# 4 Energy-accounting for Android app energy optimisation

Energy transparency can be applied in software optimisation in many ways. In this section we describe a case study in energy-aware program optimisation in Android app development. The approach is based on manual optimisations guided by a fine-grained energy model of Android source code. The overall approach is as follows.

- We utilize the methodology described in [LG15] to construct the operation-based sourcecode-level *energy model*, which is achieved by analyzing the data produced in a range of well-designed execution cases.

- The model generates *energy accounting* at operation and block level, which captures the energy characteristics of the code.

- We *focus manual optimisation* efforts on the most costly blocks, where we refactor the code to remove, reduce or replace the expensive operations, meanwhile maintaining its logical consistency with the original code.

The experimental result shows that our approach is able to save from 6.4% to 50.2% of the overall energy consumption depending on different scenarios.

Table 1: Examples of Energy Operations

| Operation            | Identified where:                         |

|----------------------|-------------------------------------------|

| Method Invocation    | one method is called                      |

| Parameter_Object     | Object is one parameter of the method     |

| Return_Object        | the method returns an Object              |

| Addition_int_int     | addition's operands are integers          |

| Multi_float_float    | multiplication's operands are floats      |

| Increment            | symbol "++" appears in code               |

| And                  | symbol "&&" appears in code               |

| Less_int_float       | "<"'s operands are integer and float      |

| Equal_Object_null    | "=="'s operands are Object and null       |

| Declaration_int      | one integer is declared                   |

| Assign_Object_null   | assignment's operands are Object and null |

| Assign_char[]_char[] | assignment's operands are arrays of chars |

| Array Reference      | one array element is referred             |

| Block Goto           | the code execution goes to a new block    |

"Energy operations" are the basic units in the source code that consume energy; all statements, blocks and methods are made up of a energy operations. In our experiment, we have 120 operations. This a fine-grained compare to other approaches to modelling energy at source code level. Energy information at the level of source lines or methods is useful; however, information at source line level could not distinguish energy consumption of two operations in the same source line, for example, which can be captured by modelling energy operations.

# 4.1 Case study outline

Our target platform is an Android development board with two ARM quad-core CPUs, and the source code in our study is a game engine used in games, demos and other interactive applications. We evaluate the approach in three game scenarios, and the experimental result shows that it can save varying amounts of energy in different scenarios. The full details of the architectural setup, the design of execution cases for energy modelling and the model construction can be found in Attachment D4.2.7. We examine three different typical scenarios in user interaction during game-playing, based on which we are able to capture the energy characteristics and optimise the source code in three different scenarios, namely Click & Move, Orbit and Waves.

Table 2: Examples of Library Functions

| Class       | Function                                  |

|-------------|-------------------------------------------|

| ArrayList   | add, get, size, isEmpty, remove           |

|             | $glBindTexture,\ glDisableClientState$    |

|             | $glDraw Elements,\ glEnable Client State$ |

| GL10        | glMultMatrixf, glTexCoordPointer          |

|             | glPopMatrix, glPushMatrix                 |

|             | glTexParameterx, glVertexPointer          |

| Math        | max, pow, sqrt, random                    |

| FloatBuffer | position, put                             |

### **4.1.1** Basic Energy Operations

Energy operations are identified directly from source code. The enumeration of the operations is inspired by Java semantics [BR15], which specifies the operational meaning, or behaviour, of the Java language, which is the target language in the experiment. We intuitively identify semantic operations that perform operations on the state and may be energy-consuming, and let them be our energy operations. Operations that turn out to have little or no energy effect will automatically be identified by the regression analysis in the later stage of the energy modelling. Table 1 lists 14 representative operations out of a total of 120 in the experiment. They include arithmetic calculations like *Multi\_float\_float, Addition\_int\_int*, in which operands types are explicit, as well as *Increment* whose operand is implicitly an integer. Boolean operations and comparisons, such as *And, Less\_int\_float* and *Equal\_Object\_null* also form one major part. *Method Invocation* and *Block Goto* are important for the control flow which plays a key role in the execution of the code. Assignments and *Array Reference* will unexpectedly take a significant amount of the application's energy consumption.

The application also employs a diversity of library functions that may be written in different languages and at lower levels of the software stack. On the other hand, usually a limited number (67 in the experiment) of library functions are frequently called in one application. So we treat them as basic modelling units. The examples of highly-used library functions in the experiment are shown in Table 2. For instance, the functions in the class of *GL10* are responsible for graphic computing.

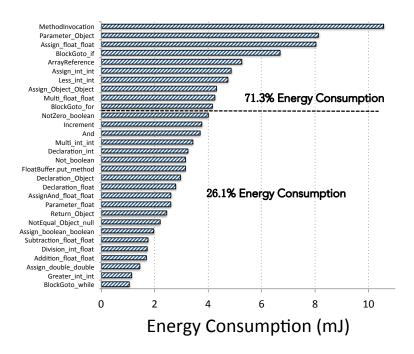

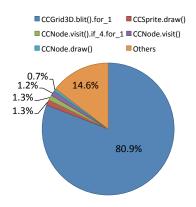

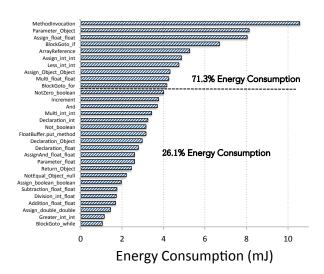

Figure 3: The top 30 energy consuming operations in Click & Move scenario.

#### 4.1.2 Energy Model

An energy model is constructed (see Attachment 4.2.X for details) yielding an energy value for each energy operation. Using this model, together with logs from the test cases used to build the energy model, we can discover many useful pieces of information about the game-engine code. The energy model of app source code based on energy operations facilitates comprehensive *energy accounting* at different levels of granularity and from various viewpoints. For example, we can identify the most energy-expensive operations and source code blocks.

#### 4.2 The Click & Move Scenario

We first consider optimising the energy in the Click & Move Scenario. We use energy accounting at operation and block level, according to which we improve the most costly blocks by removing, reducing or replacing the most expensive operations. Later in Section 4.3 and Section 4.4, when we talk about the Orbit and Waves scenarios, we will briefly introduce the energy characteristics of the code and use larger part for the code improvements.

**Operation Level.** Figure 3 shows the top 30 energy consuming operations, which are ranked by their single-execution energy costs. The section marked "71.3% Energy Consumption" shows

the percentage of the sum of costs of the top 10 operations in the total cost, considering their different numbers of executions in the Click & Move scenario, while "26.1% Energy Consumption" means the percentage of operations from 11th to 30th. The percentages indicate that the energy-usage of the code is largely determined by a relatively small number of operations, because these operations are both frequently used and expensive themselves. The 30 operations out of 187 (including library functions) take up 97.4% of the whole cost of the code, in which the top 10 consumes the major part with a percentage of 71.3%.

Usually, it is supposed that the complex arithmetic operations, such as multiplications and divisions, should be the most costly. However, the result shows that in terms of source code operations, *Method Invocation* ranks the highest. This is because *Method Invocation* involves a sequence of operations, such as storing the return address and managing the stack frame, while instance methods are always implicitly passed a "this" reference as their first parameter.

Unexpectedly, only one arithmetic operation, *Multi\_float\_float*, is a member of the top 10, and there are only six arithmetic operations in the top 30. They together cost only 6.1% of the overall energy consumption of the application, which is contrary to our intuition.

We will see later in block-level energy accounting that assignments, comparisons and *Array Reference* play significant roles in the overall energy consumption. This is not only because they are frequently used, but also because they are costly in themselves, as shown in Figure 3.

Block Goto operations are expensive as well. Based on the types of conditionals and loops where "Block Goto" occurs, they are classified into BlockGoto\_if, BlockGoto\_for and BlockGoto\_while. The result shows that they cost different amounts of energy as operations themselves, respectively 6.7 mJ, 4.1 mJ, 1.1 mJ. And together with Method Invocation, they take up 37.6% of the total energy consumption of the application.

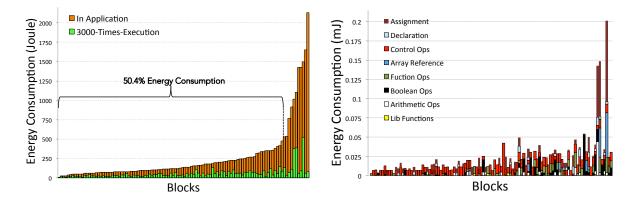

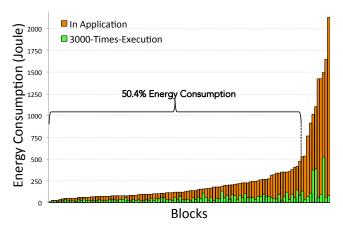

**Block Level.** In the execution cases, we have 108 active blocks with a wide diversity of energy usage. As shown in Figure 4a, "In Application" here means running the Click & Move scenario with the full set of blocks. The costs of blocks "In Application" are plotted as orange bars. Note that, blocks here obviously have distinct execution times. The cost of a fixed number (3000) of executions of one block are calculated by multiplying its single-execution cost by 3000. This could help us compare the single-execution costs of different blocks. The costs of blocks at "3000-Times-Execution" are plotted as green bars.

Similar to energy distribution on operations, a small number (11 blocks) of all the blocks uses up nearly half of the entire cost, which indicates that putting efforts on optimising a small group of blocks can achieve significant energy-saving.

There are two factors that make one block costly "In Application". The first factor is a large number of executions. For example, the most costly block "In Application" (the rightmost

(a) Block costs "In Application" and at "3000- (b) Energy proportions of different kinds of opera-Times-Execution". tions in blocks.

Figure 4: Energy distribution in Click & Move. Blocks are sorted by the order of their runtime energy costs "In Application".

orange bar in Figure 4a) has a large number of execution times. This block takes only 30.6 mJ for single-execution but 2128.6 J when running "In Application". The second factor is the energy consumption of the block itself. For example, the three prominent green bars in Figure 4a, whose single-execution costs are 201.5 mJ, 146.9 mJ and 142.8 mJ. We will later zoom in these three blocks to see which operations contribute to their energy costs.

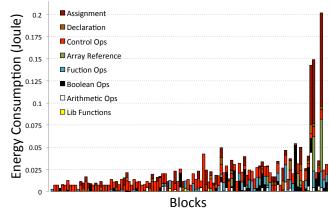

We can further observe the energy proportions of operations in each block in Figure 4b. To illustrate, operations are grouped into eight classes. Specifically, the "Block Goto" operations and *Method Invocation* are gathered in *Control Ops*; the parameter passing and the value returns of methods are in *Function Ops*; the comparisons and Booleans are in *Boolean Ops*; all the arithmetic computations are in *Arithmetic Ops*; all the library functions are in *Lib Functions*.

Most of the blocks cost less than 25 mJ for single-execution. In these blocks, *Control Ops* occupy the major part of the energy consumption, in contrast, *Arithmetic Ops* only take a tiny proportion.

For those three most prominent blocks, assignments and *Array Reference* are the biggest energy consumers. Furthermore one of the three blocks has the largest proportion of *Arithmetic Ops* among all the blocks.

The most expensive block "In Application" consists of three even parts: *Control Ops, Function Ops* and *Boolean Ops*. This block is the main entrance of the game engine to draw and display frames, so its works are conditional judgments and method invocations.

Table 3: The top 10 most costly blocks in Click & Move.

| Block ID                                | #Executions | Energy Cost (J) |

|-----------------------------------------|-------------|-----------------|

| CCNode.visit()                          | 19462       | 2128.6          |

| CCNode.transform()                      | 18903       | 1648.4          |

| CCTextureAtlas.putVertex()              | 2119        | 1494.4          |

| CCNode.visit().if_4.for_1               | 16880       | 1426.8          |

| CCNode.transform().if_1                 | 19664       | 1426.3          |

| CCTextureAtlas.putTexCoords()           | 2120        | 1107.8          |

| $CCAt las.update Values (). for \_1 \\$ | 2173        | 1018.7          |

| CCNode.visit().if_3.for_1               | 8356        | 915.7           |

| CCSprite.draw()                         | 8594        | 766.9           |

| CCTexture2D.name()                      | 13085       | 537.5           |

#### 4.2.1 Code optimisation

Both the correctness of software, and its energy-efficiency are primary design goals for app developers. In our case study our energy-aware programming approach is to focus on correctness first and then apply energy optimisations after correct working code is obtained. Clearly, a more comprehensive energy-aware development process would consider energy efficiency from the start, in choosing algorithms and data structures. However we show now that in our case study considerable optimisations are obtained from code that has been developed without energy-efficiency in mind.

The overview of energy-aware programming approach is firstly finding the most costly blocks, where we analyze the energy breakdown among the operations, and make changes to the code to remove, reduce or replace the costly operations.

We look into the top 10 costly blocks "In Application" (see Table 3). For example, *CC-Node.visit()* is the entrance block of the *visit()* function; *CCNode.visit().if\_4.for\_1* is the body block of the for loop. These 10 blocks are distributed in seven methods, so the code review does not require heavy labor. We find four easy optimisation opportunities in blocks, such as *CCNode.visit()*, *CCNode.visit().if\_4.for\_1* and *CCTexture2D.name()*. There are also other opportunities in other blocks for saving energy, but requiring more efforts and gaining little. For example, *CCAtlas.updateValues().for\_1* has several busy arithmetic expressions. Usually it is believed that replacing the busy expression with a variable could reduce energy cost, however in this case the overhead of variable declaration counteracts the energy-saving.

The four opportunities to improve the code are very simple and effective, but can only be discovered by the operation-level energy information. The changes will be shown as following.

## **Program 1** Simplified parts of **original** code in *CCNode.visit()*

```

if (children_ != null) {

if_body1;

}

draw(gl);

if (children_ != null) {

if_body2;

}

```

#### **Program 2** The changed Program 1

```

if (children_ != null) {

if_body1;

draw(gl);

if_body2;

} else {draw(gl);}

```

**If Combination.** This change is made in the most costly block *CCNode.visit()*, which has two comparisons, two Boolean operations, one *Method Invocation* and one parameter passing. In fact, the two if headers make the same comparison, as shown in Program 1. We change the code to Program 2, which combines the two if statements and meanwhile keep it logically consistent with Program 1. By these means each execution of the block can reduce one comparison, and when the condition is false, it can additionally reduce one *BlockGoto\_if*.

#### **Program 3** Simplified parts of **original** code in *CCNode* class

## **Program 4** The changed Program 3

**Inner-Class Method Inline.** When "In Application", the *transform()* function is invoked 18903 times and mostly by the *visit()* function. We change the Program 3 to Program 4 by inserting the body of *transform()* into *visit()*, meanwhile remaining the original *transform()* function in case that other parts of the code call it. This change can largely decrease the number of *transform()*'s *Method Invocations* that are very expensive. However, it may be at the cost of losing readability of the code, which could also be compensated by adding explanatory comments.

**Loop-Invariant Code Motion.** *CCNode.visit().if\_3.for\_1* and *CCNode.visit().if\_4.for\_1* are entrance blocks of the two for loops as seen in Program 5. These two loops have a quantity, *children\_.size()*, which is computed in each iteration but the value is constant. We thus hoist it outside the loop, as shown in Program 6, which can vastly save the energy of invoking and executing the *size()* function during every iteration. At the same time, we move the declaration of the *child* outside the loop, considering the cost of *Declaration\_Object* is about 2.97 mJ and also in the top 30.

**Inter-Class Method Inline.** *CCTexture2D.name()* is the 10th most costly block and costs 537.5 J "In Application". However, its job is to simply get the value of the private member variable, *\_name*, of the class *CCTexture2D*. This method has only two callers in the code. So we consider to make this variable public and let the two callers directly get access to the variable, which avoids the cost of *Method Invocation*. This change may harm the encapsulation of data, however, only one member of one class is changed. The trade-off between energy-saving and data encapsulation will be decided in the end by developers.

# **Program 5** The full version of Program 2

## **Program 6** The changed Program 5

```

CCNode child = new CCNode(); //added

int children_size = children_.size(); //added

if (children_!= null) {

for (int i=0; i<children_size; ++i) { //changed

child = children_.get(i); //changed

if (child.zOrder_{-} < 0) {

child.visit(gl);

} else

break;

}

draw(gl);

for (int i=0; i<children_size; ++i) { //changed

child = children_.get(i); //changed

if (child.zOrder_- >= 0) {

child.visit(gl);

}

} else {draw(gl);}

```

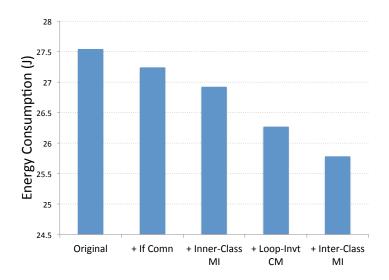

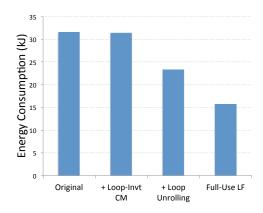

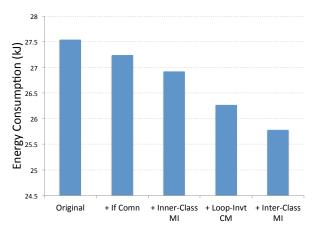

Figure 5: Energy consumption of the code without and with the changes in Click & Move.

#### 4.2.2 Evaluation

Figure 5 illustrates the energy consumption of the software without and with the changes introduced in the previous section. From left to right, the bars indicate cumulative effects of the changes. For example, "+ *If Comn*" is the energy consumption of the code with "If Combination"; "+ *Inner-Class MI*" is the energy consumption of the code with the changes of both "If Combination" and "Inner-Class Method Inline". Totally, these four simple changes save 6.4% of the entire energy consumption without influencing the functionality of code. These changes are made in the basic part of the game engine, which most applications will use heavily, so any gain here can have fundamental impact. Furthermore, these changes are made with little knowledge about the algorithm of code, the developers who wrote the code are surely able to improve the code much more and achieve more energy-saving.

#### 4.3 The Orbit Scenario

In this section, we briefly introduce the energy characteristics of Orbit scenario. Afterward, we improve the most costly blocks according to the types of expensive operations. In Section 4.3.3, we can see that the improvement can save as much as 50.2% of the overall energy consumption.

#### 4.3.1 Energy Accounting

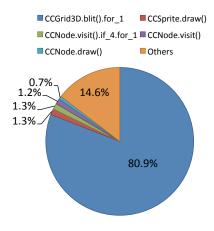

In the Orbit scenario, the block *CCGrid3d.blit().for\_1* dominates the overall energy consumption. As shown in Figure 6, 80.9% of the entire cost is consumed by this block. The second

Figure 6: In Orbit scenario, the energy proportions of blocks "In Application".

costly block consumes only 1.3%. "In Application" here means running the Orbit scenario without removing any block. Later in Section 4.3.2, we will barely put attention on this single block, requiring fairly little effort to achieve improvements.

## 4.3.2 Code optimisation

Program 7 shows the original code of *CCGrid3D.blit().for\_1*. In this block, the *Control Ops* (*BlockGoto\_for* and *Field Reference*) use up 35.6% energy; *Boolean Ops* use up 20.5%; the assignments use up 16.7%; *Arithmetic Ops* use up 14.0%; *Lib Functions* use up 13.3%. We find three easy changes to reduce or replace the expensive operations.

**Loop-Invariant Code Motion.** In this block, the value of *vertices.limit()* is constantly 2112, we thus hoist it outside the loop and replace it with the variable *limit*, as shown in Program 8. This change avoids calls of *vertices.limit()* and at the same time decreases a small amount of *Field Reference*.

**Loop Unrolling.** Also as shown in Program 8, we duplicate the loop body eight times, which reduces the times of comparisons, *BlockGoto\_fors*, assignments and additions. Note that, we set the value of increment as 24 since 24 is a factor of the *limit*, 2112.

**Full-Use of Library Function.** The job of Program 7 or Program 8 is getting all the elements in *vertices* one by one and putting them into *mVertexBuffer* one by one. The whole Program 7 in fact can be replaced by simply one line: *mVertexBuffer.put(vertices.asReadOnlyBuffer())*, which means putting the entire *vertices* into *mVertexBuffer*. This change realizes the same functionality

using the already existing library function, which is one of the key library functions already compiled into native code.

#### **Program 7** The **original** code of *CCGrid3D.blit().for\_1*

```

for (int i = 0; i < vertices.limit(); i=i+3) {

mVertexBuffer.put(vertices.get(i));

mVertexBuffer.put(vertices.get(i+1));

mVertexBuffer.put(vertices.get(i+2));

}</pre>

```

#### **Program 8** The changed Program 7

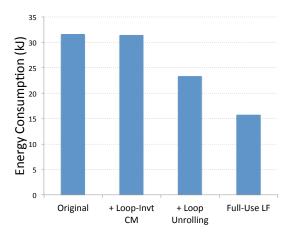

#### 4.3.3 Evaluation

Figure 7 shows the cumulative effects of the code changes on energy consumption. Exceptionally, "Full-Use LF" does not take previous changes into account and means only replacing Program 7 with the built-in library function as stated above. We can see that loop-invariant code motion does not gain much energy saving because the vertices.limit() which is a library function as well uses a very small percentage of energy consumption. On the other hand, loop unrolling achieves 25.8% energy saving due to the reduction of amount of Control Ops, comparisons and assignments, which occupy most of the cost. And the most effective change is the replacement to a library function, saving 50.2% energy consumption because this library function has been complied into native code before execution, in contrast the java source code need run-time interpretation which is not free from energy consumption. The result indicates that it is a good

Figure 7: Energy consumption of the code without and with the changes in Orbit.

Table 4: In the Waves scenario, the top 10 costly blocks "In Application" and energy percentages of different kinds of operations in each block.

| Block ID                        | #Execs | Joules | Assi. | Decl. | Cont. | Func. | Bool. | Arit. | Libr. |

|---------------------------------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| CCGrid3D.blit().for_1           | 112193 | 8094.1 | 16.7% | 0%    | 35.6% | 0%    | 20.5% | 14.0% | 13.3% |

| CCVertex3D.CCVertex3D()         | 40219  | 5232.0 | 27.2% | 0%    | 10.0% | 62.8% | 0%    | 0%    | 0%    |

| CCWaves3D.update().for_1.for_1  | 34604  | 4088.7 | 10.7% | 0%    | 32.1% | 0%    | 14.7% | 39.0% | 2.2%  |

| ccGridSize.ccg()                | 42275  | 3769.1 | 0%    | 0%    | 32.1% | 67.9% | 0%    | 0%    | 0%    |

| CCGrid3DAction.setVertex()      | 31856  | 3285.4 | 14.6% | 7.8%  | 30.9% | 46.7% | 0%    | 0%    | 0%    |

| CCGrid3DAction.originalVertex() | 36566  | 2891.3 | 19.1% | 10.2% | 40.3% | 30.4% | 0%    | 0%    | 0%    |

| CCNode.getGrid()                | 49119  | 2145.1 | 0%    | 0%    | 58.1% | 41.9% | 0%    | 0%    | 0%    |

| ccGridSize.ccGridSize()         | 10570  | 1173.8 | 30.3% | 0%    | 31.6% | 38.0% | 0%    | 0%    | 0%    |

| CCGrid3D.setVertex()            | 3944   | 657.2  | 10.1% | 1.6%  | 32.8% | 28.9% | 0%    | 26.4% | 0.2%  |

| CCGrid3D.originalVertex()       | 2785   | 374.2  | 14.0% | 1.9%  | 33.4% | 17.9% | 0%    | 32.8% | 0%    |

idea for developers to make a good use of library functions rather than implementing the same function themselves with java source code.

# 4.4 The Waves Scenario

In this section, similarly, we first analyze the energy characteristics of the blocks in the Waves scenario, based on which we modify the code and then evaluate the effects of changes on energy consumption.

#### 4.4.1 Energy Accounting

Unlike the Orbit scenario where only one block dominates energy consumption, in Waves scenario, the costs of top seven blocks are at the same order of magnitude of kJ, as listed in Table 4. The *CCGrid3D.blit().for\_1* is also employed in this scenario and is the most costly as well among all the blocks. The majority of blocks in Table 4 are directly or indirectly invoked by *CCWaves3D.update().for\_1.for\_1*, as shown in Program 9. And their jobs are mostly to set or get the values of member variables, so a large part of energy consumption goes to assignments and *Function Ops*. It was not expected that the code spends such a large amount of energy on simple setter and getter functions.

#### **Program 9** The **original** code in *CCWaves3D.update()*

#### **Program 10** Program 9 after Method Inline & Code Motion

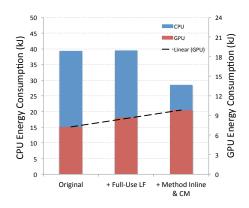

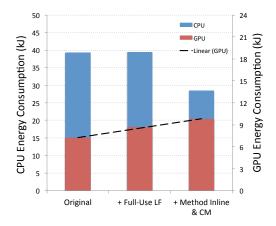

Figure 8: CPU and GPU Energy consumption of the code without and with the changes in Waves.

## 4.4.2 Code optimisation

**Full-Use of Library Function.** We have referred to the optimisation for *CCGrid3D.blit().for\_1* in Section 4.3.2 where we replace the entire Program 7 with the one-line code, which makes use of library functions. We keep this change in this scenario. For other blocks, we come up with one modification as following.

**Method Inline & Code Motion.** As shown in Program 9, the three functions called in the inner loop body are *CCGrid3DAction.originalVertex()*, *ccGridSize.ccg()* and *CCGrid3DAction.setVertex()*, which respectively cost 2891.3 J, 3769.1 J and 3285.4 J "In Application". Note that, *CC-Grid3DAction* is the parent class of *CCWaves3D*, so *originalVertext()* and *setVertex()* can be directly called without referring to their class names. As seen in Program 10, we unpack these three methods in this block: the first and fourth "added" lines are unpacked *ccGridSize.ccg()*; the second "added" and first "changed" lines are unpacked *CCGrid3DAction.originalVertex()*; the second "added" and second "changed" lines are unpacked *CCGrid3DAction.setVertex()*. This change removes all the *Method Invocations*, parameter passing and value returns related to these three functions invoked by this block. Note that, the first three "added" lines are located outside the loop in order to reduce energy consumption of the process of initializing objects and calling *CCNode.getGrid()*.

#### 4.4.3 Evaluation

Figure 8 shows the cumulative effects of changes on energy consumption of CPU and GPU (note that previous figures only showed the CPU energy consumption because the GPU energy

consumption did not vary noticeably before), and the dashed line indicates the linear trend of the GPU energy consumption. In the case of game, usually the aimed frame rate is 60 Hz, when the game overloads CPU, the frame rate will decrease, and when the workload is light, even very light, the frame rate is generally fixed to 60Hz. The frame rate in "Original" is around 36Hz; that in "+ Full-use LF" is around 50Hz; that in "+ Method Inline & CM" is around 60Hz. The change of Full-Use LF (full use of library function) does not save energy for CPU since the execution of original Waves actually overloads the CPU capacity, so the improvement of code enhances the performance and enables the device to generate more frames every second. Consequently, the GPU does more work and consumes more energy, as seen in Figure 8. After this change, when we apply the method inline and code motion, 27.7% of the overall CPU energy is saved, and for the same reason GPU consumes slightly more. This experimental result shows that our approach not only saves energy but also potentially boosts performance, which benefits users doubly.

#### 4.5 Conclusion

We proposed an energy-aware programming approach for mobile app development, which is guided by an operation-based source-code-level energy model (the construction of which is described in detail in the attachment). The general steps of the approach are as following: 1) we construct the operation-based energy model by mining the data generated in a range of well-designed execution cases; 2) based on the model, we capture the energy characteristics of the code; 3) we improve the code by removing, reducing or replacing the expensive operations in the costly blocks.

We evaluated this approach on a real-world game engine and on a physical Android development board with two ARM quad-core CPUs. The experimental result shows that our approach has a significantly positive impact on energy-saving. For different scenarios, this approach can save energy by from 6.4% to 50.2%. The result also indicates that the performance of code is a by-product as well of this approach, which potentially improves user experience more.

The optimisations were achieved by focusing on the mostly energy-consuming parts of the code, as identified by an energy accounting process. The optimisations are manual and therefore it is vital to know that they are being applied where they can have the most effect.

The approach sometimes suggests a trade-off between the code structure and energy saving. In other words, some optimisations cause the structure of the code to be lost (for example breaking encapsulation). For example, in certain cases, we could unpack some thin methods that are highly-invoked in the code, at the cost of losing the integrity of the structure of the code to some extent. This choice is an important one which the energy-aware developer should understand, and depends to some degree on whether the code in question has to be modified and maintained.

# 5 Dynamic optimisations: energy-aware scheduling in multicore environments

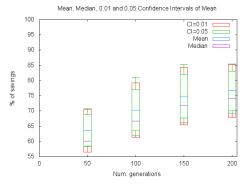

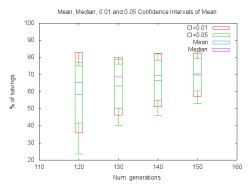

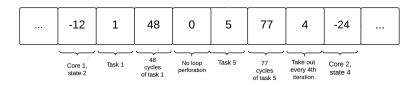

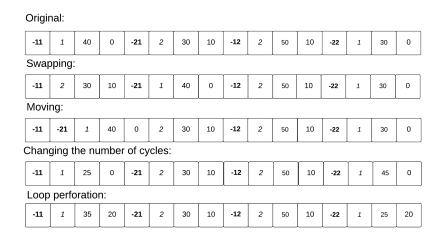

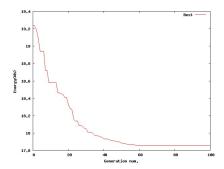

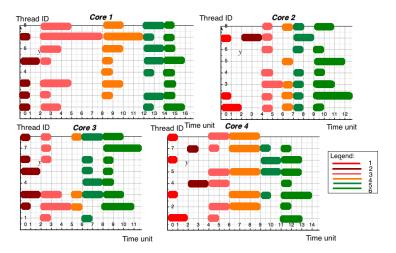

We have developed dynamic optimisation techniques for achieving energy efficient scheduling and allocation of tasks in multicore multithreaded environments with the possibility of voltage and frequency scaling. We have developed a framework for a multiobjective Evolutionary Algorithm (EA), where the objectives are energy and execution time, such that both may be subject to some constraints, given in terms of energy budgets or task deadlines [BLG13] (also as attachment D4.2.6 in this document). Based on this framework, different versions of the algorithm were implemented in order to address different types of problems:

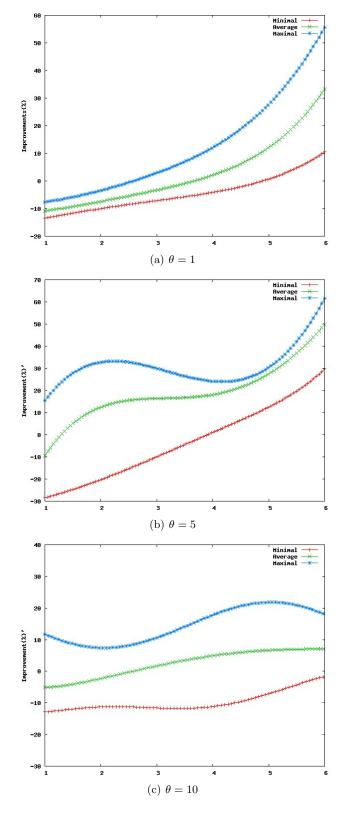

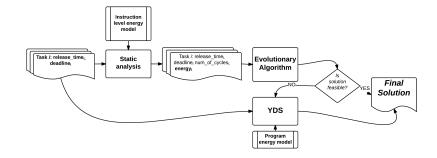

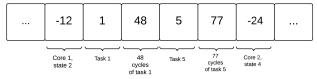

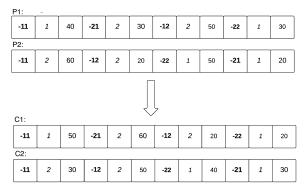

- 1. *Deterministic algorithm*. The time and power of the tasks are expressed as deterministic values, which are obtained either by profiling or by static analysis at compile time. The energy of the whole schedule has been estimated either using a low level energy model of the targeted platform [BLG15a] (attachment D4.2.2), or by using static analysis [BLLG15a] (attachment D4.2.5). Different versions of this algorithm include:

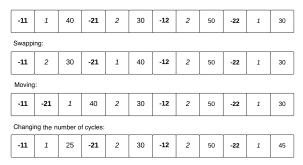

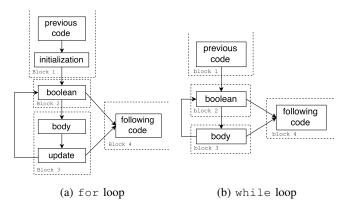

- Possibility to introduce *task migration and preemption*, i.e., the execution of a task can be stopped before finishing, and can be resumed afterwards on the same or different thread or core [BLG15a, BLLG15a, BLLG15b] (attachments D4.2.2, D4.2.5 and D4.2.3).

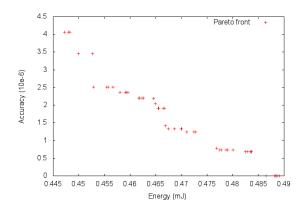

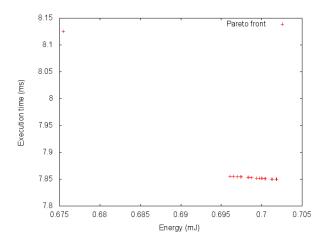

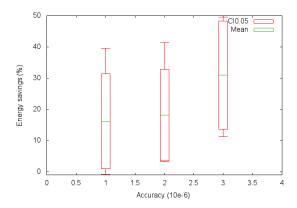

- Possibility to *decrease accuracy in order to save energy* in applications that permit certain level of accuracy loss. Accuracy loss has been implemented through loop perforation, where for a previously defined (set of) loop(s), we skip every nth loop iteration [BLLG15b] (attachment D4.2.3).

- 2. Stochastic scheduling. We have proven that if the actual values of the power and execution time of the tasks are different from the estimations used to create the deterministic scheduler, the resulting scheduler does not have to be optimal in terms of energy and execution time. In this situation it is better to represent execution time and power as random variables with their corresponding distribution, and optimise the expected values of the energy and/or execution time of the scheduler. Two variations of this work have been implemented, based on the following assumptions:

- The tasks are independent [BLG15c] (attachment D4.2.1).

- The tasks are dependent [BLG15b] (attachment D4.2.4). In this case the dependence has been modelled using copula theory, and it has been proven that more optimal results are achieved when modelling existing dependency.

- 3. *Modified YDS Algorithm* [BLLG15a] (attachment D4.2.5). YDS is a well known algorithm for task scheduling when the voltage and frequency can be scaled. Yet, it was invented in the 90s, and the hardware platforms have changed significantly since then. Multicore chips are practically a standard nowadays, while YDS was created for single core, and the static power forms a growingly important part of the total power consumption of a chip. To overcome these issues, we have performed two improvements: a) a method to stop decreasing voltage and/or frequency before the point the total power starts increasing again, and b) different methods to allocate tasks on different cores, which are then scheduled on each core using separate YDSs. In comparison with the EA algorithm, YDS is much faster, however, the final schedule provided by EA is much more optimal in terms of energy.

In all of the mentioned algorithms above it is very important to have an estimation of the resource consumption of a task, where the resource can be time or energy. For this purpose, we have greatly relied on the static analysis techniques implemented in the CiaoPP tool. Depending on the nature of the scheduling, i.e., if the deadlines or the energy budgets are hard (always have to be met), or soft (do not have be met all the time), we can use either average or worst case estimations. For the case of worst case estimations, which are both safe and accurate, we have combined evolutionary algorithms and static analysis.

Although the algorithms have been adapted for multicore multithreaded XMOS chips, they can be easily adapted to any multicore environment, including large scale data centers. Given that many tasks running in the datacenter at the same time are not related, the developed algorithms can be parallelized and efficiently executed using for example the *MapReduce* algorithm. On the other hand, experiments with static analysis have demonstrated that any a priori knowledge about resource consumption of a task, or a program, can provide better results in terms of additional energy savings: we have seen that the EA scheduler, which used both time and energy estimations, performs much better in terms of energy savings than the YDS algorithm, which uses only time estimations.

## References

- [BLG13] Z. Banković and P. Lopez-Garcia. Genetic Algorithm-based Allocation and Scheduling for Voltage and Frequency Scalable XMOS Chips. In *Hybrid Artificial Intelligent Systems (HAIS 2013)*, volume 8073 of *Lecture Notes in Computer Science*, pages 401–410. Springer, 2013.

- [BLG15a] Z. Banković and P. López-García. Energy Efficient Allocation and Scheduling for DVFS-enabled Multicore Environments using a Multiobjective Evolutionary Algorithm. In Genetic and Evolutionary Computation Conference, GECCO 2015, Companion Material Proceedings, pages 1353–1354. ACM, 2015.

- [BLG15b] Z. Banković and P. López-García. Improved Energy-aware Stochastic Scheduling based on Evolutionary Algorithms via Copula-based Modeling of Task Dependences. In Álvaro Herrero, Javier Sedano, Bruno Baruque, Héctor Quintián, and Emilio Corchado, editors, International Conference on Soft Computing Models in Industrial and Environmental Applications (SOCO 2015), volume 368 of Advances in Intelligent Systems and Computing, pages 153–163. Springer International Publishing, 2015.

- [BLG15c] Zorana Banković and Pedro Lopez-Garcia. Stochastic vs. Deterministic Evolutionary Algorithm-based Allocation and Scheduling for XMOS Chips. *Neurocomputing*, 150:82–89, February 2015.

- [BLLG15a] Z. Banković, U. Liqat, and P. López-García. A Practical Approach for Energy Efficient Scheduling in Multicore Environments by combining Evolutionary and YDS Algorithms with Faster Energy Estimation. In *The 11th International Conference on Artificial Intelligence Applications and Innovations (AIAI'15)*, volume 458 of *IFIP Advances in Information and Communication Technology*, pages 478–493. Springer International Publishing, 2015.

- [BLLG15b] Z. Banković, U. Liqat, and P. López-García. Trading-off Accuracy vs. Energy in Multicore Processors via Evolutionary Algorithms Combining Loop Perforation and Static Analysis-based Scheduling. In Enrique Onieva, Igor Santos, Eneko Osaba, Héctor Quintián, and Emilio Corchado, editors, *Hybrid Artificial Intelligent Systems (HAIS 2015)*, volume 9121 of *Lecture Notes in Computer Science*, pages 690–701. Springer International Publishing, 2015.

- [BR15] Denis Bogdanas and Grigore Roşu. K-java: A complete semantics of java. *SIG-PLAN Not.*, 50(1):445–456, January 2015.

- [LG15] Xueliang Li and John P. Gallagher. Fine-grained energy modeling for mobile application source code. Technical report, Roskilde University, December 2015. submitted for publication.

# **Attachments**

# Attachment D4.2.1

Stochastic vs. Deterministic

Evolutionary Algorithm-based

Allocation and Scheduling for XMOS

Chips

Published in Neurocomputing, Vol. 150, pages 82–89, Elsevier, February 2015.

ELSEVIER

#### Contents lists available at ScienceDirect

### Neurocomputing

journal homepage: www.elsevier.com/locate/neucom

# Stochastic vs. deterministic evolutionary algorithm-based allocation and scheduling for XMOS chips

Zorana Banković <sup>a,\*</sup>, Pedro López-García <sup>a,b</sup>

- <sup>a</sup> IMDEA Software Institute, Madrid, Spain

- <sup>b</sup> Spanish Council for Scientific Research (CSIC), Spain

#### ARTICLE INFO

Article history:

Received 18 November 2013

Received in revised form

9 April 2014

Accepted 15 June 2014

Available online 2 October 2014

#### Keywords:

Deterministic and stochastic scheduling Multiprocessor multithreaded architectures Dynamic voltage and frequency scaling Evolutionary algorithms Multi-objective optimization

#### ABSTRACT

We present an approach based on multi-objective evolutionary algorithms for the automatic scheduling and allocation of tasks in a multiprocessor multithreaded architecture, together with an assignment of the appropriate voltage and frequency of each processor in a way the overall energy consumed by the execution of the tasks is optimized and all task deadlines are met. We have implemented both a deterministic scheduling algorithm, where the execution time and the energy consumption of different tasks have a known deterministic value, and a stochastic scheduling algorithm, where the execution time and energy are treated as random variables with corresponding probability density functions, given that in reality these values can vary significantly due to numerous reasons. It is assumed that execution time and energy consumption estimations, both for the deterministic and the stochastic case, are obtained by a static analysis process. It has already been proven for the case of makespan optimization that the stochastic scheduling is underestimated by its deterministic counterpart, and that in many real world situations, the stochastic scheduler outperforms the deterministic one. In this work we prove that for the tested scenario the stochastic scheduler for energy optimization outperforms its deterministic counterpart improving energy consumption by 15.4% in the best case.

© 2014 Elsevier B.V. All rights reserved.

#### 1. Introduction

The most common approach for solving the problem of optimal task scheduling is to use a safe estimation of the values that the function to be optimized depends on, such as the execution time of each task or its power consumption. When such estimation gives a single (numeric) value for execution time (and power/energy), we refer to the problem as the deterministic scheduling. However, the execution time of a task in reality can vary considerably, due to a number of reasons, e.g. unknown memory access time, operating system effects that cannot be known in advance, etc. For this reason, it is more accurate to treat execution time, as well as energy consumption, which is closely related, as a random variable with a corresponding probability density and/or cumulative distribution function. We refer to this group of problems as stochastic scheduling problems. Moreover, there are state-of-the-art results of optimal scheduling for makespan optimization [1,2] that prove that in certain situations the deterministic scheduler provides results that significantly deviate from the optimal ones, and that better results can be obtained using stochastic scheduling. In this

*E-mail addresses*: zorana.bankovic@imdea.org (Z. Banković), pedro.lopez@imdea.org (P. López-García).

work we prove that this is also the case for energy consumption optimization.

Our objective is to optimize the energy consumption through scheduling and allocation of a set of tasks running on multiprocessor/multicore<sup>1</sup> and multithreaded voltage and frequency scalable architectures designed by XMOS [3]. In such XMOS chips, threads are pipelined in four stages, where in each stage of the pipeline one instruction from a different thread is executed, so in essence we can say that the threads also run in parallel. Thus, we deal here with two levels of parallelism: multicore with multiple threads on each of them. Furthermore, the XMOS chips have the possibility to dynamically scale voltage and frequency, which can significantly contribute to energy consumption optimization, as we will explain in the following.

The dynamic power consumption due to the switching activity in digital CMOS circuits can be expressed with the following formula:

$$P = \alpha \cdot C_{eff} \cdot V^2 \cdot f$$

where  $C_{eff}$  is the effective capacitance, V the voltage supply, f the operating frequency, and  $\alpha$  the switching factor. If we decrease the

<sup>\*</sup> Corresponding author.

<sup>&</sup>lt;sup>1</sup> These two terms are interchangeable throughout this paper.

voltage supply and the operating frequency, the dynamic power will decrease significantly. Moreover, the static power, which is the result of the leakage currents, also decreases quadratically with the voltage [4]. Thus, voltage and frequency decrease can achieve significant power and energy savings. This optimization technique is known as Dynamic Voltage and Frequency Scaling (DVFS). However, voltage and frequency decrease slows down the operation of the circuit, and has to be applied in a way the required timing deadlines of all the tasks are still met. Furthermore, the process of scaling voltage and/or frequency introduces additional latencies, which implies that we have to develop a set of requirements that define the applicability of this approach.

Regarding the application of DVFS to the XMOS chips, we assume that different processors/cores can have different (V, f) settings, while the threads running on the same processor/core at the same time must have the same (V, f) setting. We also assume that the wake-up time is big enough in relation to the execution times of the tasks to avoid the shutdown of separate processors. However, as we will see, our approach can be easily extended to take into account the possibility of shutdown.

Given a set of tasks and their corresponding deadlines, our objective is to provide a scheduling and allocation, and also assign voltage and frequency to each processor in a way the total energy consumption is optimized, while meeting the task deadlines. We assume that the tasks are heterogeneous, and they in general have different starting times and deadlines. We further assume that there is no precedence between tasks, and no preemption. Regarding the estimation of the corresponding values for execution time and power/energy consumption, in the deterministic case we assume that there are available analysis tools that give us such estimations, which are a necessary input to the scheduling algorithms we present here. Since this work has been done in the context of the ENTRA project [5], where tools for the estimation at compile time of the energy consumption and execution time of programs are being developed, we have direct access to such tools. For example, we can use the energy analyzer of the CiaoPP tool [6] already developed. In addition we could also use any existing timing analysis tools, for which great amount of work have been devoted. On the other hand, an ongoing work in the ENTRA project [5] is dedicated to deriving probability functions of both execution time and energy consumption, as well as the interdependence between different variables that represent time and energy of different tasks, which is the necessary input to the stochastic scheduler.

In general, the problem of scheduling and allocation is NP-hard. For this reason, different heuristic algorithms have been developed that are capable of obtaining sub-optimal solutions in real time, such as [7], which is based on Artificial Bee Colony for makespan minimization and machine occupation maximization, or [8], which compares the performances of a hybrid genetic algorithm, a hybrid simulated annealing and particle swarm optimization for the flow shop scheduling problem in a manufacturing supply chain. Many of these heuristic approaches use evolutionary algorithms (EAs), e.g. [9] for the vehicle routing problem, and in particular genetic algorithms (GAs) [10-12]. An EA is a well-known bio-inspired approach based on the principle of the survival of the fittest. Its most important advantage is a fast exploration of the search space, which allows the quick finding of acceptable solutions. This is the reason our scheduler is based on EAs. Since DVFS reduces energy, but increases execution time, these two magnitudes are clearly in conflict. For this reason, we use a multi-objective optimization approach, in order to find a tradeoff between energy consumption and execution time. We also provide an appropriate representation of solutions that captures the two levels of parallelism, i.e., at both processor and thread level, and at the same time performs allocation and scheduling and identifies appropriate (V, f) settings in real time, exploring in this

way the entire search space. As far as we know, the work presented in this paper is the first solution to mentioned type of problems.

The rest of the paper is organized as follows. Section 2 presents the most relevant related work and emphasizes the most important advantages of our approach. Section 3 details the sources of power consumption in CPUs and sets up the constraints that are the basis for generating a solution. Section 4 explains the problem that is being solved and points out the main differences between deterministic and stochastic scheduling. Section 5 details the implemented approach, while Section 6 explains the experimentation environment and presents the most significant results. Finally, Section 7 draws the most important conclusions and gives some directions for future work.

#### 2. Related work

The related work to the one presented here falls into a great variety of topics, yet the ones with the closest relation are energy-aware scheduling approaches using DVFS, in particular the ones based on EAs (GAs). In the following we present these techniques and emphasize the main advantages of our approach.

#### 2.1. Energy-aware deterministic scheduling

Since DVFS can provide significant energy savings, its optimal usage has been extensively studied. Some examples divide scheduling and allocation in two separate steps, such as the one given in [13], where in the first step the allocation problem is solved using Linear Programming, while in the second one the scheduling problem is solved for separate processors using Bin Packing. Another approach [10] solves the scheduling problem using a GA that integrates DVFS in the fitness function. However, such a division of the problem reduces the search space, since it becomes limited by the optimal solution of the first part of the problem, which does not always correspond to the global optimum. For this reason, we believe that better solutions can be achieved by solving the scheduling and allocation problem at the same time, while also accounting for the DVFS. There is one example of GA-based scheduling [11] that combines scheduling, allocation and power management in one process. However, it only deals with voltage scaling.

There is also a significant group of publications on using GAs for the optimal scheduling and allocation in multiprocessor systems with the DVFS feature. For example, the approach presented in [12] aims to minimize both energy and makespan as a bi-objective problem. The same problem is solved in another work [14], but using the island model of parallel GA populations. Another approach [15] treats the problem from two opposite points of view: in the first one, it optimizes the energy given the scheduler length, while in the other one it optimizes the scheduling length given the energy bound. However, none of the solutions include the possibility of two levels of parallelism as in our work, where each processor can have a number of different threads executing in parallel.

#### 2.2. Energy-aware stochastic scheduling

Stochastic scheduling has gained lots of interest over the years, since many different cases include uncertainty. In general, approaches to optimization under uncertainty include various modeling philosophies, the most important being the following ones:

- Expectation minimization.

- Minimization of deviations from goals.

- Minimization of maximum costs.

- Optimization over soft constraints.

Our approach clearly belongs to the first group. The solution presented in [16] is in the same group, however, it solves the stochastic scheduling problem by reducing it to the deterministic case. The benefit of this approach is the lower execution time, yet at the cost of decreased accuracy.

Regarding DV(F)S-based approaches, the typical ones are presented in [17,18]. The first one [17] belongs to the group that take advantage of soft constraints, in particular soft deadlines. However, it also divides the problem into two steps: in the first one it allocates cycles to tasks and schedules them to deliver performance guarantees, while in the second step it takes advantage of the soft deadlines to scale the voltage. The same approach is followed by the second GA-based work [18]. The only difference is that in this case the problem is divided into task mapping and task/voltage scheduling. As before, dividing the problem into two separate steps reduces the search space and does not always result in an optimal solution.

#### 2.3. Advantages

Having presented the most important solutions from the stateof-the-art and their issues, we can emphasize the following advantages of our approach:

- Thanks to the ENTRA project results, we can assume the availability of safe approximations of probability density functions for the execution time and power consumption, which give us the opportunity to gain higher accuracy when solving the scheduling problem.

- By considering the scheduling, allocation, and voltage and frequency assignment at the same time, we explore the complete search space, and thus we have bigger chances of finding the most optimal solution.

- 3. Finally, our approach is the only one that supports two levels of parallelism: multicore with multiple threads running on each core.

#### 3. CPU power consumption

The energy required to complete a (set of) task(s) in time T on a processor, given its clock frequency f and its voltage V, is defined by

$$E_{cpuf,V} = \int_{t_0}^{t_0+T} P_{cpuf,V}(t) dt$$

(1)

where  $P_{cpu,f,V}$  is the (time varying) power of the processor with the (V, f) setting. This power can be expressed as

$$P_{cpu,f,V}(t) = P_{cpu,V}^{fix} + P_{idle,f,V} + P_{cpu,f,V}^{act}(t)$$

(2)

where  $P_{cpu,V}^{fix}$  is the portion of the power that includes Phase Locked Loop (PLL) clock generator and leakage power consumption in the case of the XMOS chips [4], which is the part that only depends on voltage, not on frequency.  $P_{idle,f,V}$  is the power spent when the processor is not executing any application, e.g., for maintaining the clock signal active. For a certain fixed (V, f) setting, the sum of these two values does not change in time. For this reason, in the further text we will call this sum the standing power consumption, denoted  $P_{cpu,V,f}^{std}$ . This power can be easily obtained by measuring the CPU power when there are no running applications for each (V, f) setting.  $P_{cpu,V,V}^{act}$  is the active power spent on switching activity during the execution of the application(s). Thus, formula (2) can be written as

$$P_{cpu,f,V}(t) = P_{cpu,f,V}^{std} + P_{cpu,f,V}^{act}(t)$$

(3)

which used in (1) gives the energy consumed during time T:

$$E_{cpuf,V} = P_{cpuf,V}^{std} \cdot T + \sum_{i=1}^{m} P_{if,V} \cdot T_i$$

$$\tag{4}$$

where  $P_{i,f,V}$  is the power spent by the application i, which is completed in time  $T_i$ , and m is the number of threads (thus, the maximum number of applications that can be executed on one processor at any moment is m). In the case when the threads can complete more than one application within time T, formula (4) has the following form:

$$E_{cpuf,V} = P_{cpuf,V}^{std} \cdot T + \sum_{i=1}^{m} \sum_{j=1}^{k} P_{ijf,V} \cdot T_{ij}$$

(5)

where k is the maximum number of applications a thread can execute in time T, and  $T_{ij}$  is the execution time of the application j running on thread i.

#### 3.1. Introducing dynamic voltage and frequency scaling